## A Reconfigurable Low Noise Amplifier for

## a Multi-standard Receiver

A Thesis

SUBMITTED IN FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### DOCTOR OF PHILOSOPY

By

Mohd Tafir Mustaffa

То

**School of Engineering & Science**

Faculty of Health, Engineering and Science

Victoria University Australia

2009

## **Declaration of Originality**

I, Mohd Tafir Mustaffa, declare that the PhD thesis entitled "A Reconfigurable Low Noise Amplifier for a Multi-standard Receiver" is no more than 100,000 words in length including quotes and exclusive of tables, figures, appendices, bibliography, references and footnotes. This thesis contains no material that has been submitted previously, in whole or in part, for the award of any other academic degree or diploma. Except where otherwise indicated, this thesis is my own work.

Mohd Tafir Mustaffa

To my wonderful wife Khairunnisa Baruddin

and

my family.

### ABSTRACT

Mobile devices are widely used for a vast range of applications such as mobile phones, personal digital assistant, personal computers, video games console, etc. However, the performance of these devices is restricted by the support of the network and the mobile functionality and efficiency. Current applications require high data rates and global mobility which can be satisfied with the co-existence and handover between newly developed third generation (3G) or Universal Mobile Telecommunication System (UMTS) standard and current second generation (2G) standards including: Global Standards for Mobile (GSM), Digital Cellular System (DCS), and Personal Communication Systems (PCS). Therefore, recent research in wireless communication has shifted towards achieving a multi-standard terminal, which can support efficiently multiple standards including GSM/DCS/PCS/3G.

References show that currently available multi-standard receivers employ parallel architecture to accommodate multiple standards. This option, however, is bulky, costly, complex, and consumes relatively high power. To address these limitations, current research trend is to merge the parallel paths into a single path wireless receiver. Literature review shows that currently available low noise amplifier (LNA) as part of this receiver, only support combination of a few mobile communication standards. Therefore, there is a need for a new LNA architecture that could support most of the 2G and 3G standards.

Abstract

In this research, the aim is to design and implement a new LNA for a multi-standard mobile receiver based on reconfigurability concept. This research was carried out in two major parts. The first part is to design and implement wide band multi-standard multi-band LNAs for two bands of interest (lower frequency band – 800 to 1000 MHz and upper frequency band – 1800 to 2200 MHz). These two bands should cover most of the 2G and 3G standards currently in use worldwide. In this work, the design of LNA based on IDCS topology using wide band approach has been investigated, designed, implemented and approved by means of simulations, and measurement of fabricated ICs. The second part of this research, to develop a single reconfigurable multi-standard multi-band LNAs. This LNA has the capability to function in two modes of operation, either at lower band or upper band of the 2G or 3G standards.

The significance of this research is to respond to the industries need of multi-standard multi-band LNA with simple architecture. This LNA is less complex, more power efficient and cost effective compared to the parallel architecture in the design of the multi-standard RF receiver architecture. Therefore, the proposed reconfigurable LNA provides access to functions such as voice calls, video calls, multimedia messaging, online TV, video on demands, etc. at a high data rate more efficiently.

## ACKNOWLEDGEMENTS

First and foremost, I would like to express my special appreciation to my supervisor Associate Professor Dr Aladin Zayegh for his teaching, guidance, support, assistance and encouragement during this research. The opportunities and learning experiences he has given me are much appreciated. The experience at Victoria University has been especially rewarding and helpful for my future career because of his support, not only in the research work but also in many other aspects. I would also like to show my appreciation to my co-supervisors, Dr Ronny Veljanovski and Associate Professor Aleksandar Stojcevski for their timely advice and support throughout this research.

I would like to express my thanks to RMIC group from Universiti Sains Malaysia (USM), especially Dr Tun Zainal Azni Zulkifli, for their support, advice and teaching throughout this research. I cannot forget the facilities provided by CEDEC (Collaborative µElectronic Design Excellence Centre) of USM for fabrication and measurement of my LNAs, without which my research would not reach this level. Special thanks to Associate Professor Dr Othman, director of CEDEC for that opportunity. My thanks also go to Silterra Malaysia for the design kit and access to fabrication through CEDEC.

I also would like to thank my colleagues at the School of Electrical Engineering for their valuable support. In particular, I would like to thank, Amanullah Maung Than Oo, Yufridin Wahab, Hassan Al-Khalidi, Abdulrahman Hadbah, David Fitrio, Anand Mohan,

Jaideep Chandran, Nikhil Joglekar and other friends in room G218, School of Engineering and Science.

Above all, I would like to give special thanks and great appreciations to my wonderful wife Khairunnisa Baruddin and my family in Malaysia for their love, patience, understandings, sacrifices, prayers and encouragements during the research and thesis writing.

## LIST OF ABBREVIATIONS

| 2G     | Second Generation                                  |

|--------|----------------------------------------------------|

| 3G     | Third Generation                                   |

| 3GPP   | 3rd Generation Partnership Project                 |

| ADS    | Advanced Design System                             |

| BER    | Bit Error Rate                                     |

| BiCMOS | Bipolar CMOS                                       |

| BPF    | Band Pass Filter                                   |

| CEDEC  | Collaborative µElectronic Design Excellence Centre |

| CG     | Common Gate                                        |

| CMOS   | Complementary Metal Oxide Semiconductor            |

| CNR    | Carrier to Noise Ratio                             |

| CS     | Common Source                                      |

| DCR    | Direct Conversion Receiver                         |

| DCS    | Digital Cellular System                            |

| drc    | design rule check                                  |

| DUT    | Device Under Test                                  |

| EGSM   | Enhanced-GSM                                       |

| ETSI   | European Telecommunication Standards Institute     |

| GMSK   | Gaussian Minimum Shift Keying                      |

| GPS    | Global Positioning System                          |

| GSG    | Ground-Signal-Ground                               |

- IDCS Inductively-Degenerated Common Source

- IF Intermediate Frequency

- IP2 Second Order Intercept Point

- IP3 Third Order Intercept Point

- LNA Low Noise Amplifier

- LO Local Oscillator

- lvs layout versus schematic

- MEMS Micro Electro Mechanical System

- NCSU North Carolina State University

- NF Noise Figure

- NQS Non-Quasi Static

- PCS Personal Communication Systems

- pex parasitic extraction

- QPSK Quadrature Phase-Shift Keying

- RF Radio Frequency

- RFIC Radio Frequency Integrated Circuit

- SiGe Silicon Germanium

- TI Texas Instrument

- TOI Third Order Intercept Point

- UMTS Universal Mobile Telecommunication System

- USM Universiti Sains Malaysia

- UWB Ultra Wide Band

VCO Voltage Controlled Oscillator

WCDMA Wide Code Division Multiple Access

WLAN Wireless Local Area Network

## **TABLE OF CONTENTS**

| ABSTRACT              | ii   |

|-----------------------|------|

| ACKNOWLEDGEMENTS      | iv   |

| LIST OF ABBREVIATIONS | vi   |

| TABLE OF CONTENTS     | ix   |

| LIST OF FIGURES       | xiv  |

| LIST OF TABLES        | хх   |

| LIST OF PUBLICATIONS  | xxii |

#### CHAPTER 1: THESIS OVERVIEW

| 1.0 | Introduction                          | 1  |

|-----|---------------------------------------|----|

| 1.1 | Research methodologies and techniques | 6  |

| 1.2 | Organisation of the Thesis            | 9  |

| 1.3 | Originality of the Thesis             | 10 |

#### CHAPTER 2: LITERATURE REVIEW

| 2.0 | Introduction                                       |    |

|-----|----------------------------------------------------|----|

| 2.1 | Multi-standard RF systems                          | 14 |

|     | 2.1.1 RF standards                                 | 14 |

|     | 2.1.2 RF receiver architectures                    | 21 |

|     | 2.1.3 The development of RF receiver architectures | 27 |

| 2.2 | Reconfigurable Multi-standard Mobile Terminals     | 32 |

|      |       | 2.2.1     | Recent developments of reconfigurable            |    |

|------|-------|-----------|--------------------------------------------------|----|

|      |       |           | multi-standard system                            | 33 |

|      |       | 2.2.2     | Recent developments of reconfigurable            |    |

|      |       |           | multi-standard LNA                               | 37 |

|      | 2.3   | Conclus   | sion                                             | 40 |

|      |       |           |                                                  |    |

| СНАР | TER 3 | : LNA     | THEORIES AND DESIGNS                             |    |

|      | 3.0   | Introduc  | tion                                             | 42 |

|      | 3.1   | LNA the   | ories                                            | 43 |

|      |       | 3.1.1     | Impedance matching                               | 44 |

|      |       | 3.1.2     | Noise sources in CMOS                            | 47 |

|      |       | 3.1.3     | S-parameters                                     | 55 |

|      |       | 3.1.4     | Linearity                                        | 56 |

|      | 3.2   | Multi-st  | andard multi-band LNA                            | 57 |

|      |       | 3.2.1     | Multi-standard LNA                               | 57 |

|      |       | 3.2.2     | Multi-standard LNA for wide band receiver system | 59 |

|      |       | 3.2.3     | Multi-standard multi-band LNA designs            |    |

|      |       |           | using wide band approach                         | 62 |

|      | 3.3   | Multi-sta | andard multi-band LNA designs                    | 64 |

|      |       | 3.3.1     | Multi-standard multi-band LNA design flow        | 64 |

|      |       | 3.3.2     | Multi-standard multi-band LNA designs –          |    |

|      |       |           | 2 GHz with buffer                                | 66 |

|        | 3.3.3      | Multi-standard multi-band LNA designs – |     |

|--------|------------|-----------------------------------------|-----|

|        |            | 0.9 GHz with no buffer                  | 74  |

|        | 3.3.4      | Multi-standard multi-band LNA design –  |     |

|        |            | 2 GHz with no buffer                    | 80  |

| 3.4    | 4 Conclu   | sion                                    | 82  |

|        |            |                                         |     |

| CHAPTE | R 4: RESL  | JLTS AND DISCUSSION                     |     |

| 4.0    | Introduc   | ction                                   | 84  |

| 4.1    | Pre-laye   | out simulation results                  | 85  |

|        | 4.1.1      | Multi-standard multi-band LNA designs – |     |

|        |            | 2 GHz with buffer                       | 85  |

|        | 4.1.2      | Multi-standard multi-band LNA designs – |     |

|        |            | 0.9 GHz with no buffer                  | 94  |

|        | 4.1.3      | Multi-standard multi-band LNA design –  |     |

|        |            | 2 GHz with no buffer                    | 102 |

| 4.2    | 2 Post-lag | yout simulation results                 | 106 |

|        | 4.2.1      | Multi-standard multi-band LNA2 design – |     |

|        |            | 2 GHz with buffer                       | 106 |

|        | 4.2.2      | Multi-standard multi-band LNA4 design – |     |

|        |            | 0.9 GHz with no buffer                  | 109 |

|        | 4.2.3      | Multi-standard multi-band LNA5 design – |     |

|        |            | 2 GHz with no buffer                    | 112 |

| 4.3    | Discuss    | sion of the results                     | 115 |

|     | 4.4    | Conclus  | sion                                            | 120 |

|-----|--------|----------|-------------------------------------------------|-----|

| CHA | PTER { | 5: MEAS  | SUREMENT RESULTS OF THE FABRICATED LNAS         |     |

|     | 5.0    | Introduo | ction                                           | 121 |

|     | 5.1    | Measur   | rement setup                                    | 122 |

|     | 5.2    | Measur   | ement results of the fabricated LNAs            | 123 |

|     |        | 5.2.1    | Multi-standard multi-band LNA2 IC measurement – |     |

|     |        |          | 2 GHz with buffer                               | 123 |

|     |        | 5.2.2    | Multi-standard multi-band LNA4 IC measurement – |     |

|     |        |          | 0.9 GHz with no buffer                          | 132 |

|     |        | 5.2.3    | Multi-standard multi-band LNA5 IC measurement – |     |

|     |        |          | 2 GHz with no buffer                            | 141 |

|     | 5.3    | Discuss  | sion of the results                             | 153 |

|     | 5.4    | Conclus  | sion                                            | 157 |

#### CHAPTER 6: RECONFIGURABLE MULTI-STANDARD MULTI-BAND LNA

| 6.0 | Introduc                                                   | ction                                                   | 159 |

|-----|------------------------------------------------------------|---------------------------------------------------------|-----|

| 6.1 | Design and implementation of reconfigurable multi-standard |                                                         |     |

|     | multi-ba                                                   | and LNA                                                 | 160 |

|     | 6.1.1                                                      | Design consideration                                    | 160 |

|     | 6.1.2                                                      | A reconfigurable multi-standard multi-band LNA          | 162 |

|     | 6.1.3                                                      | Circuit implementation of reconfigurable multi-standard |     |

|     |                                                            | multi-band LNA                                          | 168 |

| 6.2 | Simulation results        | 172 |

|-----|---------------------------|-----|

| 6.3 | Discussion of the results | 182 |

| 6.4 | Conclusion                | 184 |

#### CHAPTER 7: CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE WORK

|      | 7.0    | Introduction                                         | 186  |

|------|--------|------------------------------------------------------|------|

|      | 7.1    | Summary and achievements of the research             | 187  |

|      | 7.2    | Recommendations for future work                      | 190  |

| REFE | RENCE  | ES                                                   | 192  |

| APPE |        | A: THE REFLECTION COEFFICIENT OF THE LOADED TRASMISS | SION |

| LINE |        |                                                      | 212  |

| APPE | NDIX E | 3: THE NON-QUASI STATIC EFFECT OF CMOS TRANSISTOR    | 214  |

| APPE |        | : PASSIVE COMPONENTS OF THE DESIGN KIT               | 216  |

**APPENDIX D:**S-PARAMETERS OF THE LNA218

APPENDIX E: LINEARITY OF THE LNA 221

## LIST OF FIGURES

| Figure 1.1:  | 3G phone with various applications [1]                         | 2  |

|--------------|----------------------------------------------------------------|----|

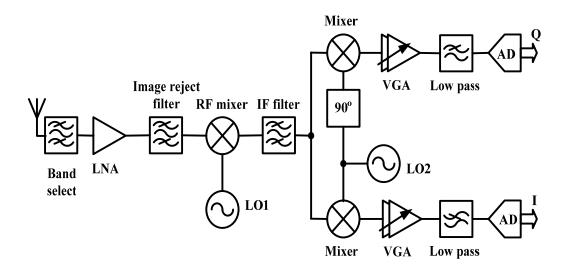

| Figure 2.1:  | Superheterodyne architecture [48]                              | 22 |

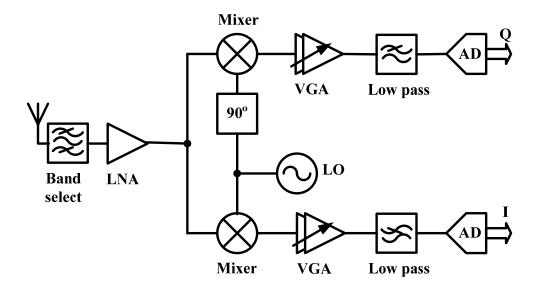

| Figure 2.2:  | Homodyne architecture [46]                                     | 24 |

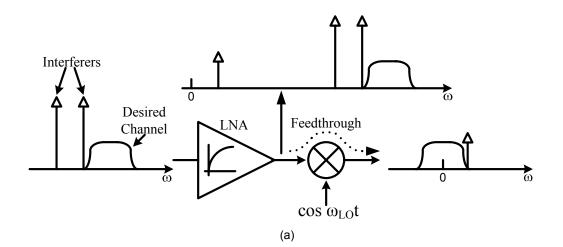

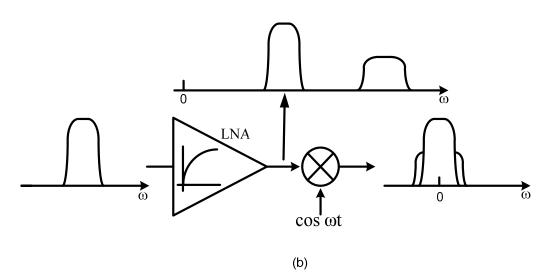

| Figure 2.3:  | Effect of even-order distortion [51]                           | 26 |

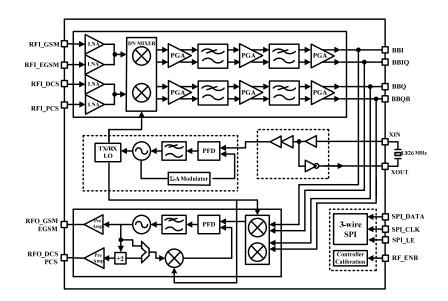

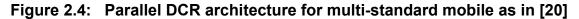

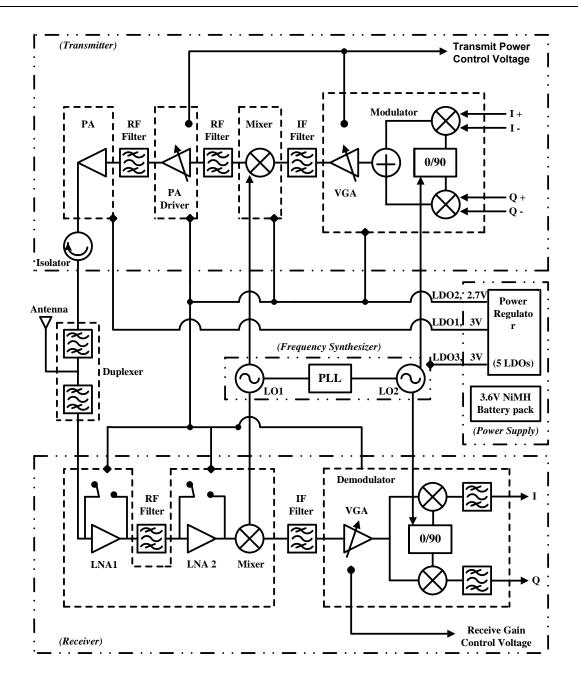

| Figure 2.4:  | Parallel DCR architecture for multi-standard mobile as in [20] | 28 |

| Figure 2.5:  | QUALCOMM chip solution (redrawn partly) [10]                   | 29 |

| Figure 2.6:  | Superheterodyne receiver as in [55]                            | 30 |

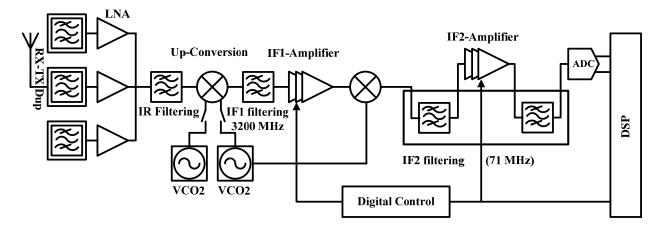

| Figure 2.7:  | Superheterodyne receiver as in [56]                            | 31 |

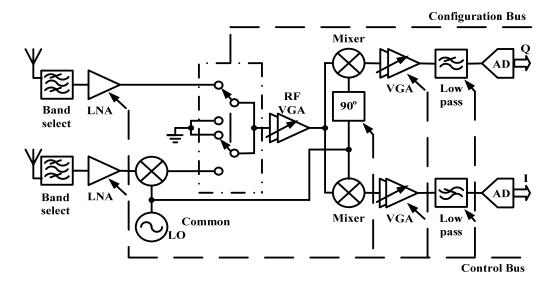

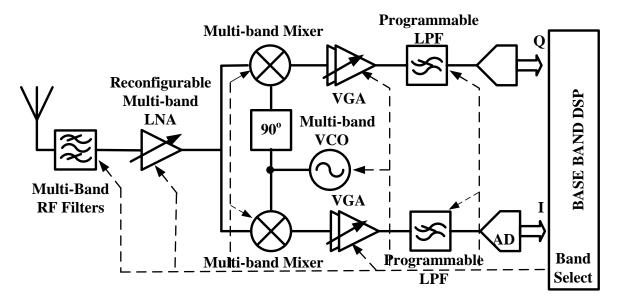

| Figure 2.9:  | Reconfigurable receiver architecture as in [65]                | 34 |

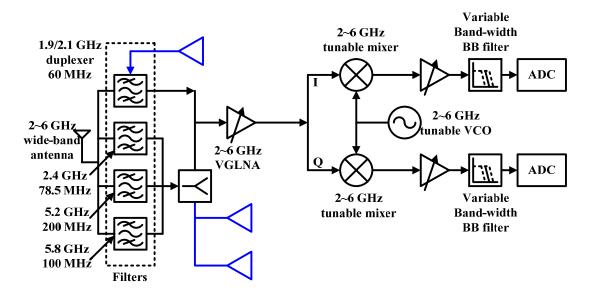

| Figure 2.10: | 2-6 GHz multi-standard receiver architecture [67]              | 34 |

| Figure 2.11: | Proposed receiver architecture                                 | 36 |

| Figure 2.12: | Multiband LNA architecture [68]                                | 38 |

| Figure 2.13: | Dual-standard LNA as in [69]                                   | 39 |

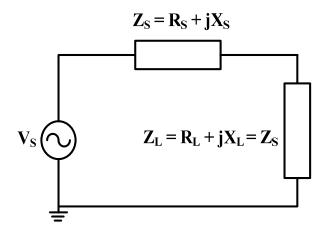

| Figure 3.1:  | Condition for impedance match                                  | 44 |

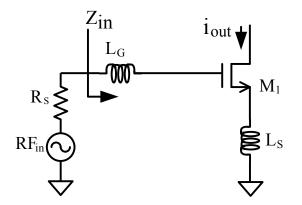

| Figure 3.2:  | Inductive source degeneration                                  | 45 |

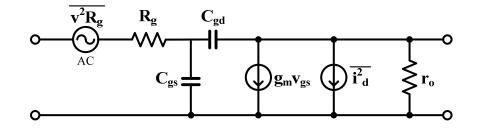

| Figure 3.3:  | Standard CMOS noise model representing thermal noise [25]      | 47 |

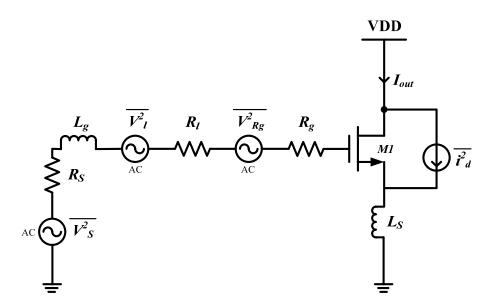

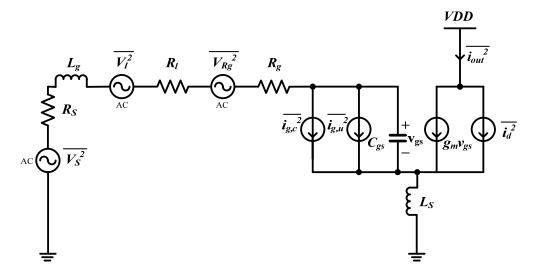

| Figure 3.4:  | IDCS circuit for input stage noise calculations [25]           | 48 |

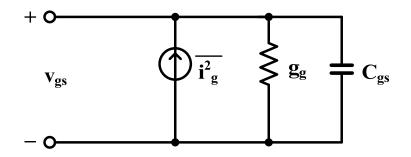

| Figure 3.5:  | Standard CMOS noise model representing induced gate noise [25] | 50 |

| Figure 3.6:  | Revised IDCS small-signal model for input stage noise          |    |

|              | calculations [25]                                              | 52 |

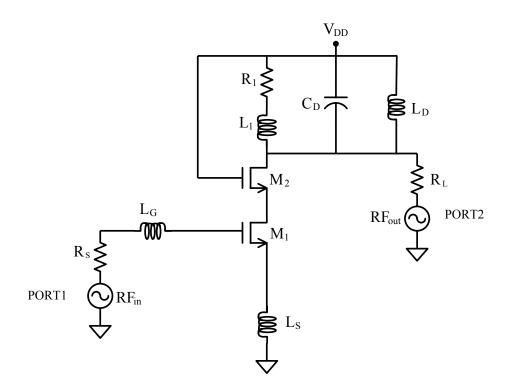

| Figure 3.7:  | Wide band IDCS LNA1 [85]                                                       | 66 |

|--------------|--------------------------------------------------------------------------------|----|

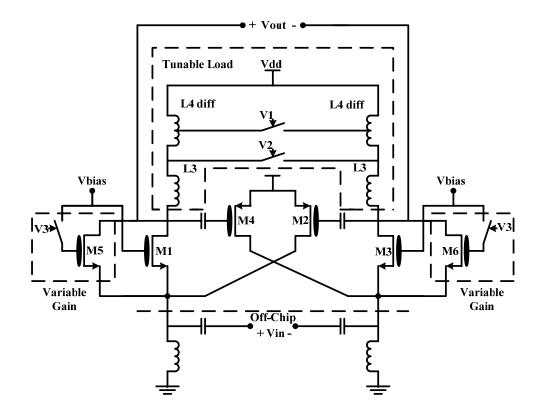

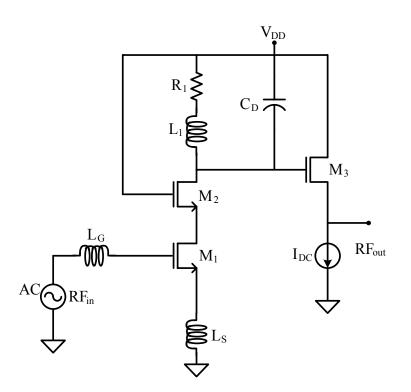

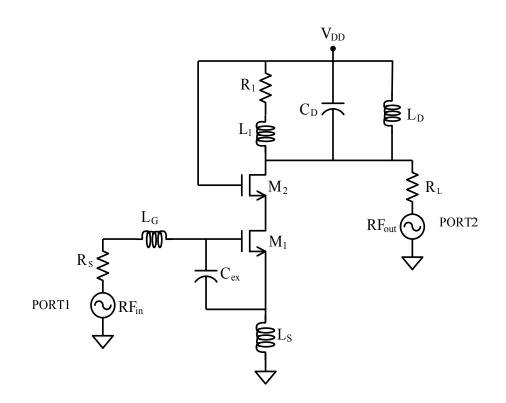

| Figure 3.8:  | Wide band IDCS LNA2 [88]                                                       | 72 |

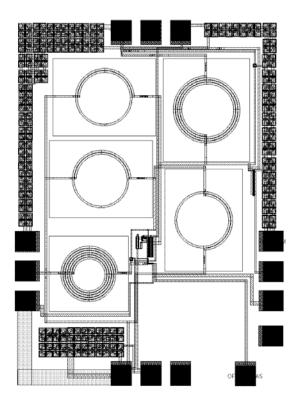

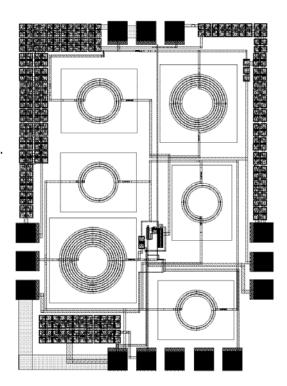

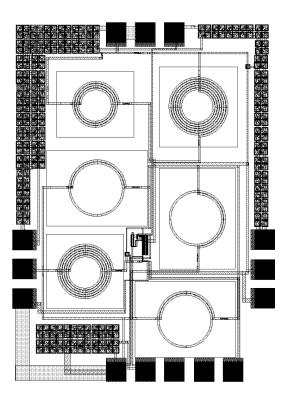

| Figure 3.9:  | Layout of CMOS LNA2 with GSG pad and DCQ pad for dc supply                     |    |

|              | and biasing voltage [88]                                                       | 74 |

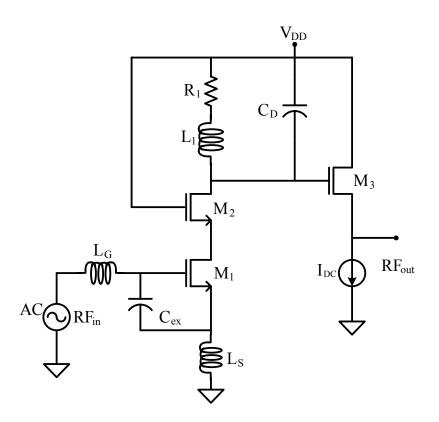

| Figure 3.10: | Wide band LNA3 [89]                                                            | 75 |

| Figure 3.11: | Wide band LNA4 [90]                                                            | 78 |

| Figure 3.12: | Layout of CMOS LNA4 with GSG pad and DCQ pad for dc supply                     |    |

|              | and biasing voltage [90]                                                       | 79 |

| Figure 3.13: | Wide band LNA5 [91]                                                            | 81 |

| Figure 3.14: | Layout of CMOS LNA5 with GSG pad and DCQ pad for dc supply                     |    |

|              | and biasing voltage [91]                                                       | 82 |

| Figure 4.1:  | Forward gain and reverse isolation of LNA1                                     | 86 |

| Figure 4.2:  | Input and output return losses of LNA1                                         | 86 |

| Figure 4.3:  | Noise figure of LNA1                                                           | 87 |

| Figure 4.4:  | IIP3 of LNA1                                                                   | 88 |

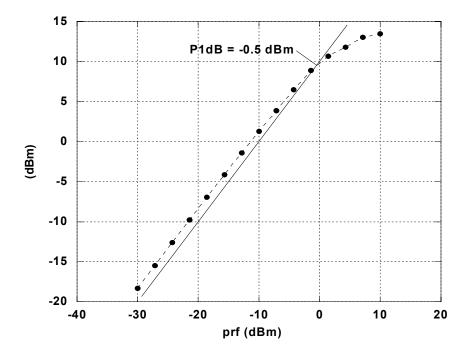

| Figure 4.5:  | P1dB of LNA1                                                                   | 89 |

| Figure 4.6:  | Forward gain and reverse isolation of LNA2                                     | 90 |

| Figure 4.7:  | Input and output return losses of LNA2:                                        |    |

|              | $S_{22}$ (a) not optimised for linearity, $S_{22}$ (b) optimised for linearity | 91 |

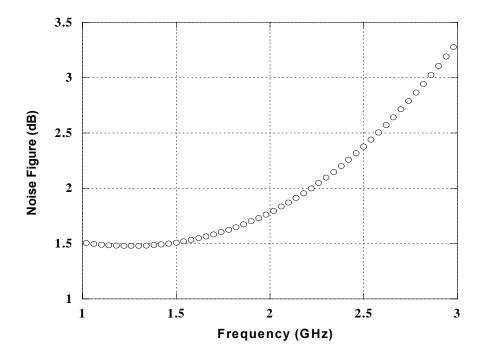

| Figure 4.8:  | Noise figure of LNA2                                                           | 92 |

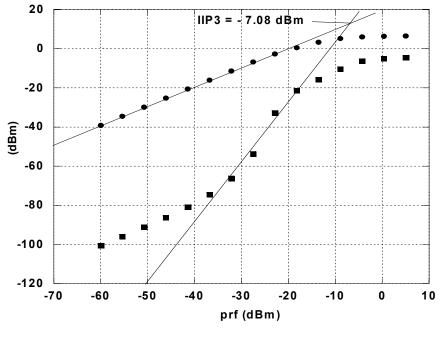

| Figure 4.9:  | IIP3 of LNA2                                                                   | 93 |

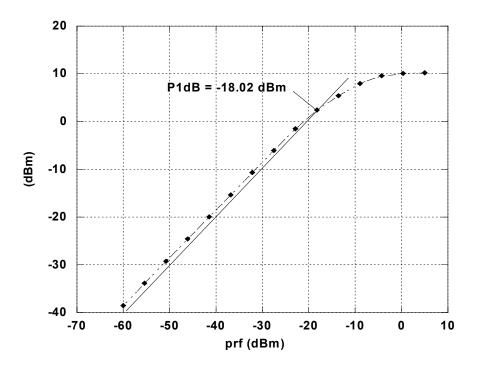

| Figure 4.10: | P1dB of LNA2                                                                   | 93 |

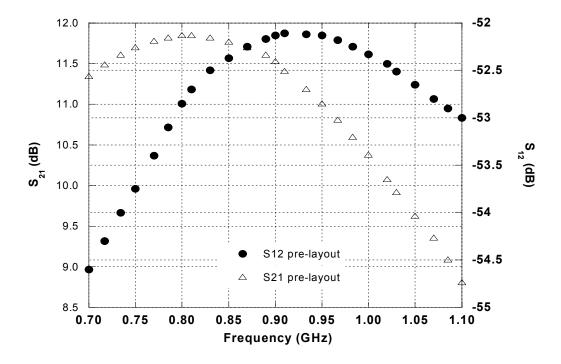

| Figure 4.11: | Forward gain and reverse isolation of LNA3                                     | 95 |

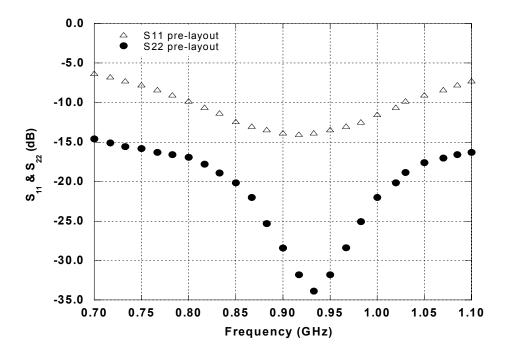

| Figure 4.12: | Input and output return losses of LNA3                 | 95  |

|--------------|--------------------------------------------------------|-----|

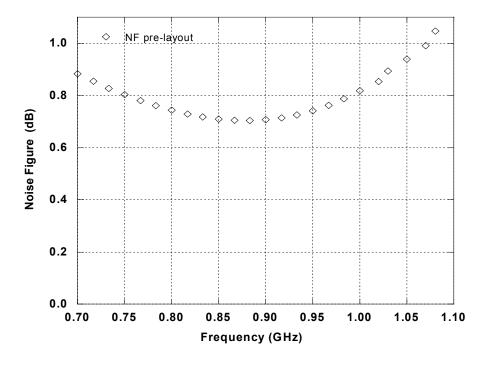

| Figure 4.13: | Noise figure of LNA3                                   | 96  |

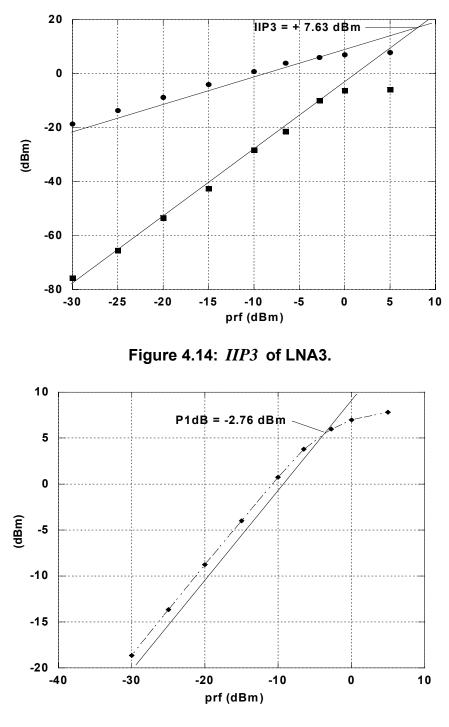

| Figure 4.14: | <i>IIP3</i> of LNA3                                    | 97  |

| Figure 4.15: | P1dB of LNA3                                           | 97  |

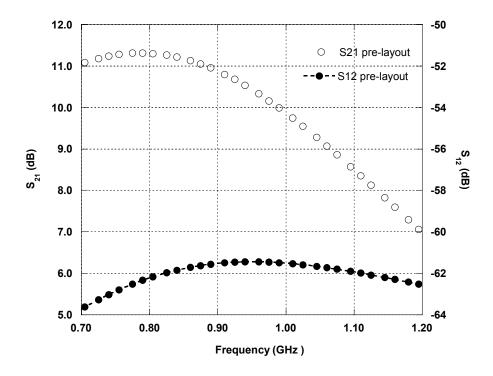

| Figure 4.16: | Forward gain and reverse isolation of LNA4             | 99  |

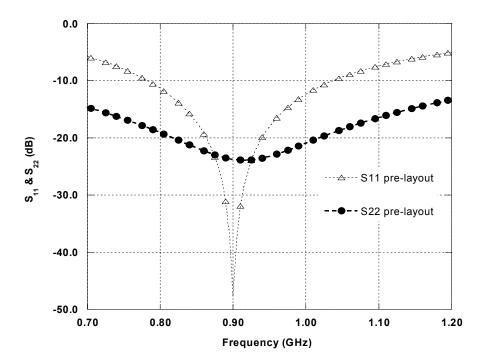

| Figure 4.17: | Input and output return losses of LNA4                 | 99  |

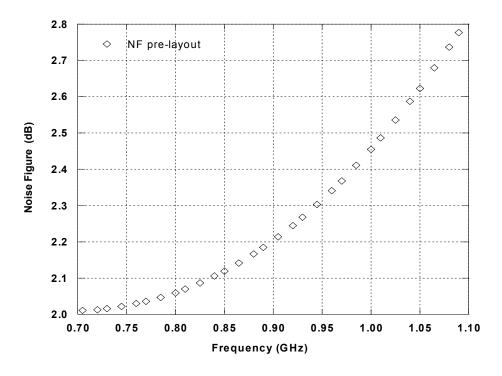

| Figure 4.18: | Noise figure of LNA4                                   | 100 |

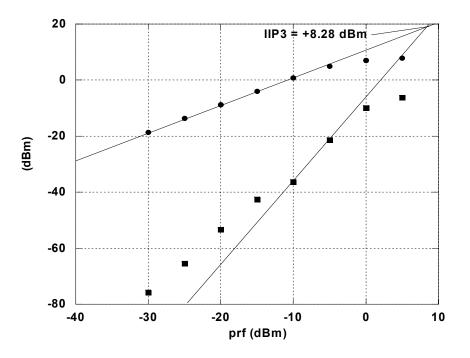

| Figure 4.19: | <i>IIP3</i> of LNA4                                    | 101 |

| Figure 4.20: | P1dB of LNA4                                           | 101 |

| Figure 4.21: | Forward gain and reverse isolation of LNA5             | 103 |

| Figure 4.22: | Input and output return losses of LNA5                 | 104 |

| Figure 4.23: | Noise figure of LNA5                                   | 104 |

| Figure 4.24: | <i>IIP3</i> of LNA5                                    | 105 |

| Figure 4.25: | P1dB of LNA5                                           | 106 |

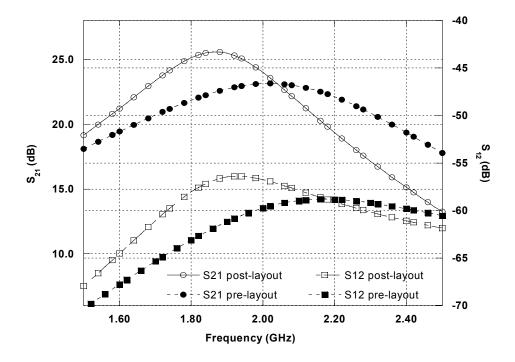

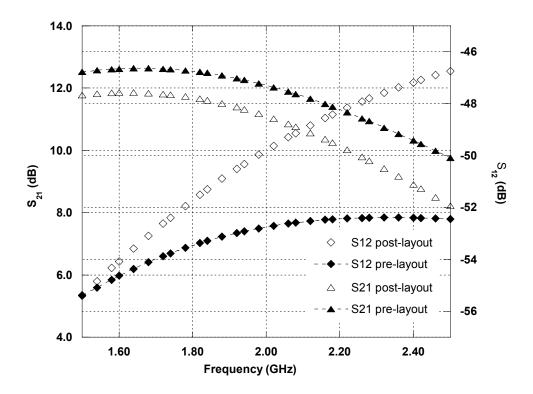

| Figure 4.26: | Post-layout forward gain and reverse isolation of LNA2 | 107 |

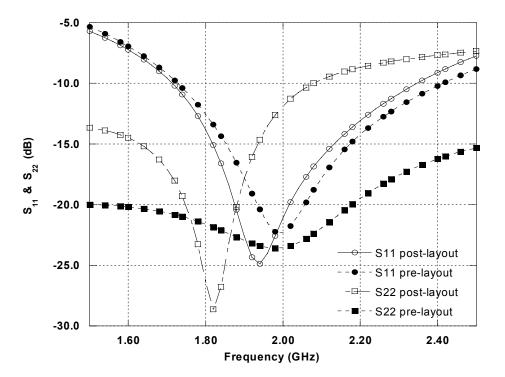

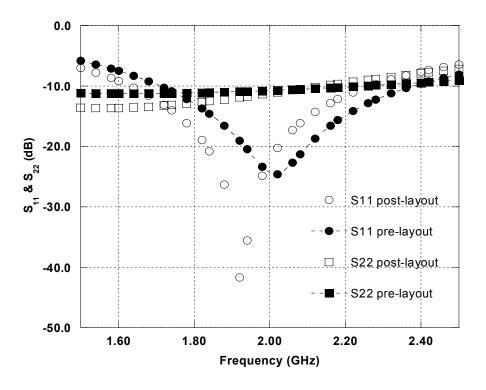

| Figure 4.27: | Post-layout input and output return losses of LNA2     | 108 |

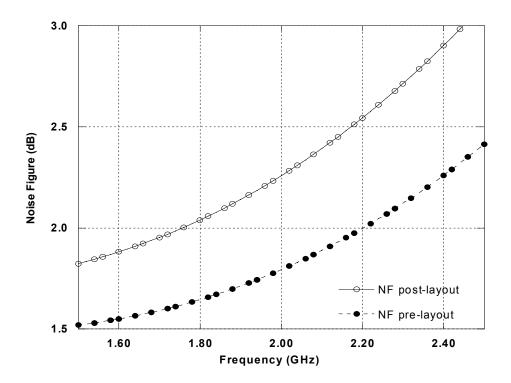

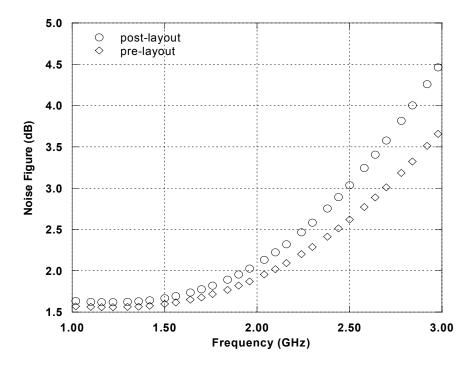

| Figure 4.28: | Post-layout noise figure of LNA2                       | 109 |

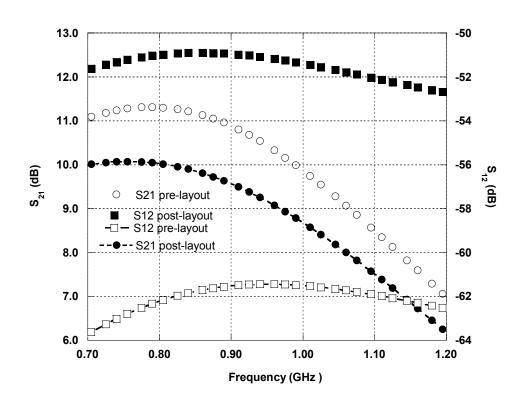

| Figure 4.29: | Post-layout forward gain and reverse isolation of LNA4 | 110 |

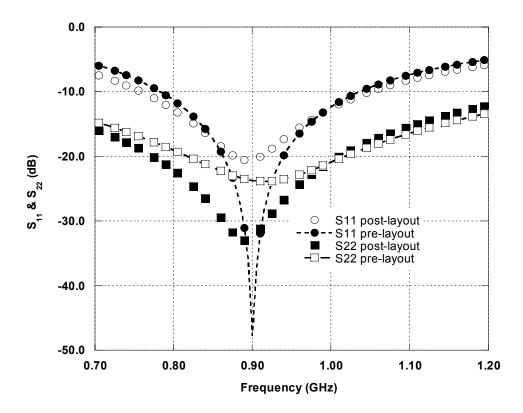

| Figure 4.30: | Post-layout input and output return losses of LNA4     | 111 |

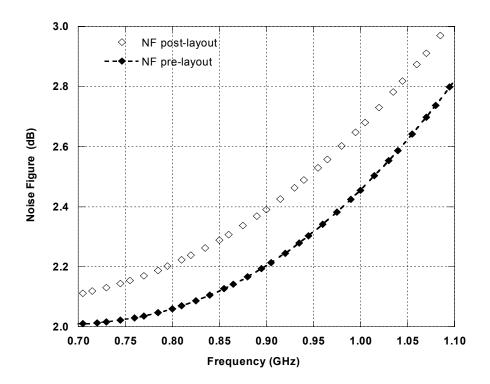

| Figure 4.31: | Post-layout noise figure of LNA4                       | 112 |

| Figure 4.32: | Post-layout forward gain and reverse isolation of LNA5 | 114 |

| Figure 4.33: | Post-layout input and output return losses of LNA5     | 114 |

| Figure 4.34: | Post-layout noise figure of LNA5                       | 115 |

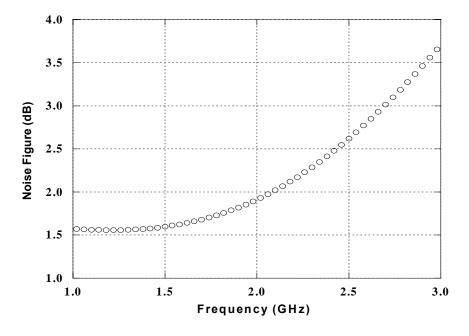

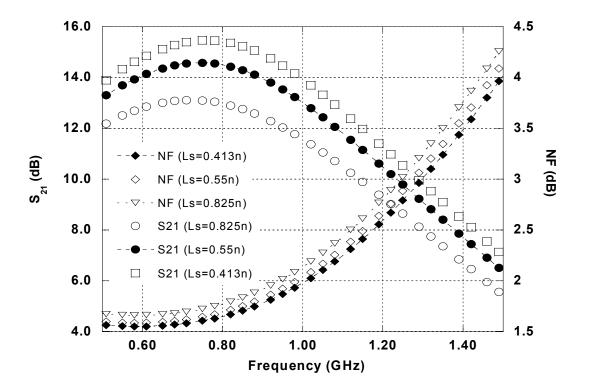

| Noise figure simulation with different values of $L_S$                       | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

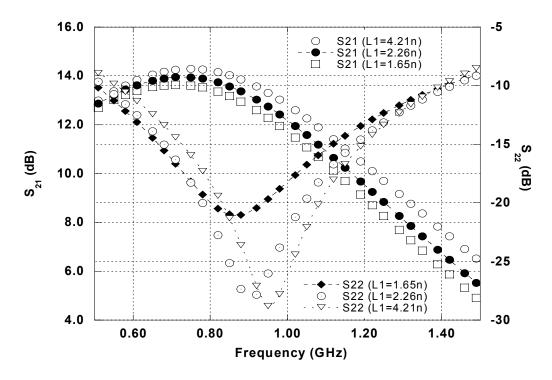

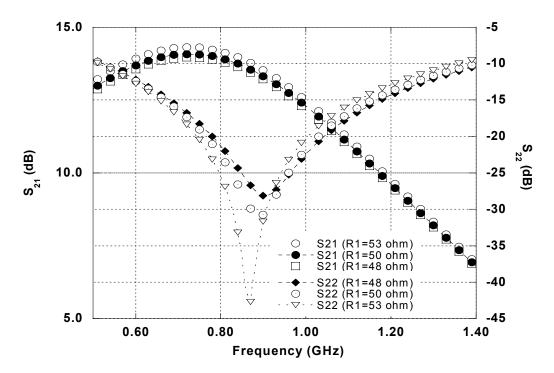

| Output return loss ( $S_{22}$ ): fix $R_I$ but different values of $L_I$     | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Output return loss ( $S_{22}$ ): fix $L_{I}$ but different values of $R_{I}$ | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

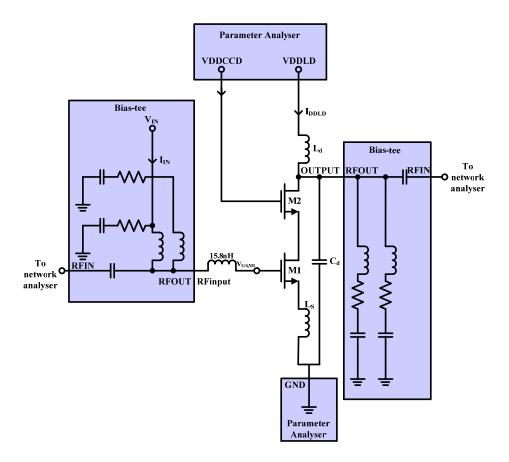

| Measurement strategy [95]                                                    | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

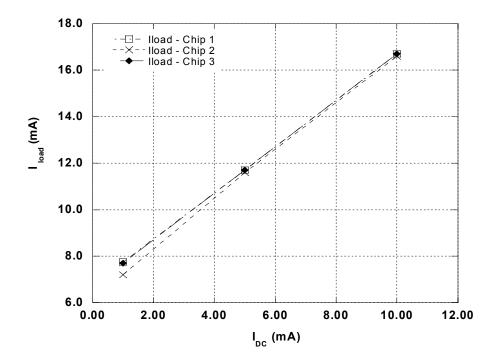

| Measured I <sub>load</sub> versus I <sub>dc</sub>                            | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

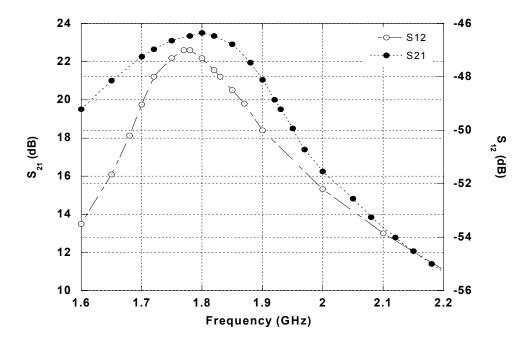

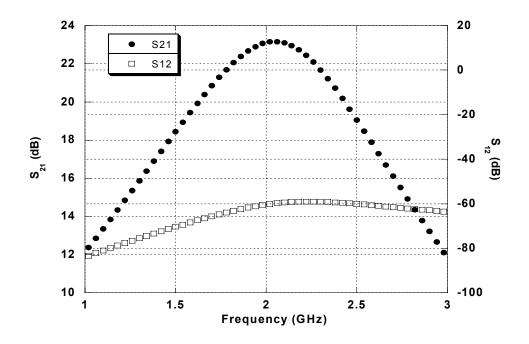

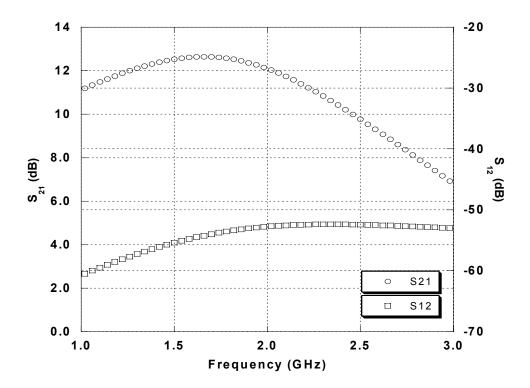

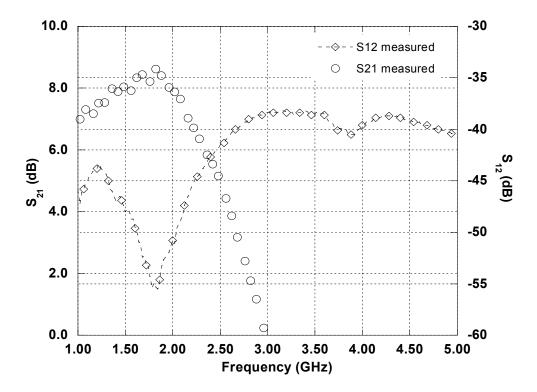

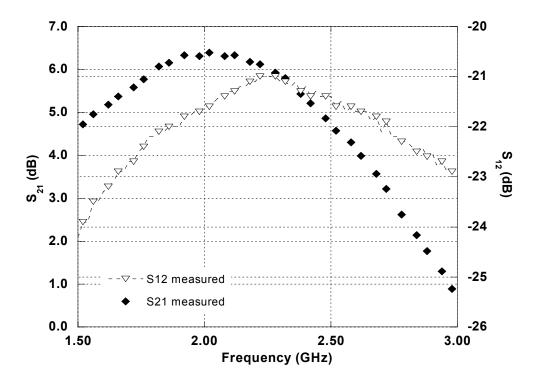

| Forward gain and reverse isolation of LNA2 with $I_{dc}$ =1mA                | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

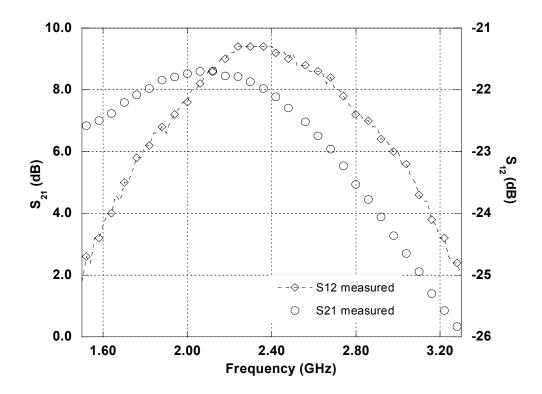

| Forward gain and reverse isolation of LNA2 with $I_{dc}$ =5mA                | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Forward gain and reverse isolation of LNA2 with $I_{\rm dc}$ =10mA           | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

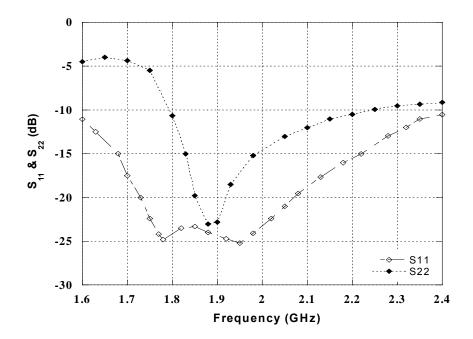

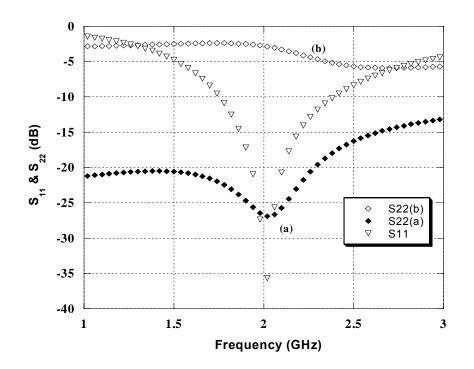

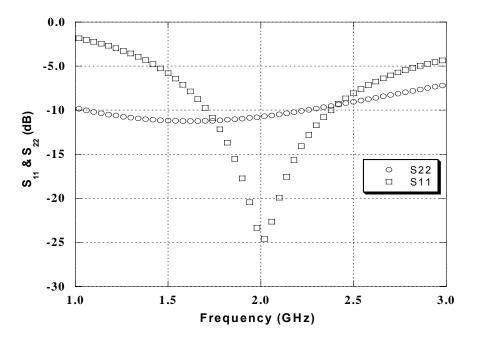

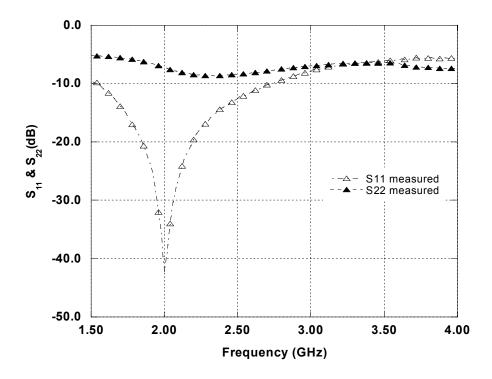

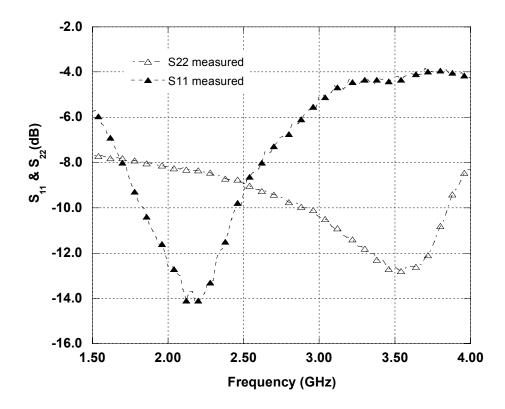

| Input and output return losses of the LNA2 with $I_{dc}$ =1mA                | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input and output return losses of the LNA2 with $I_{dc}$ =5mA                | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input and output return losses of the LNA2 with $I_{dc}$ =10mA               | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

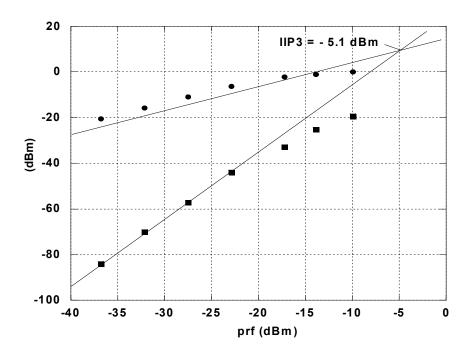

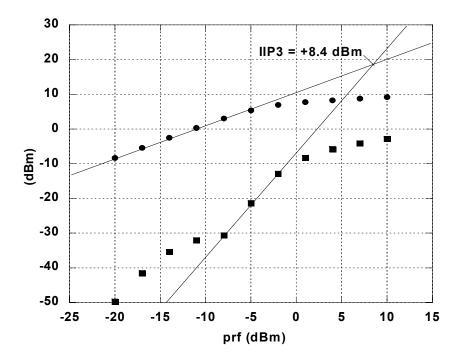

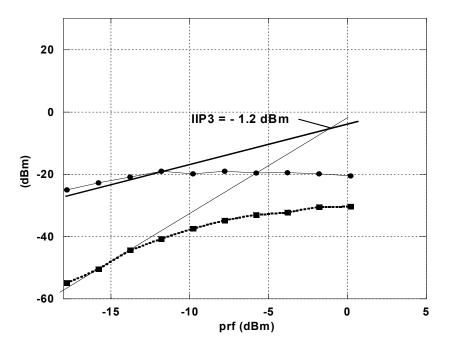

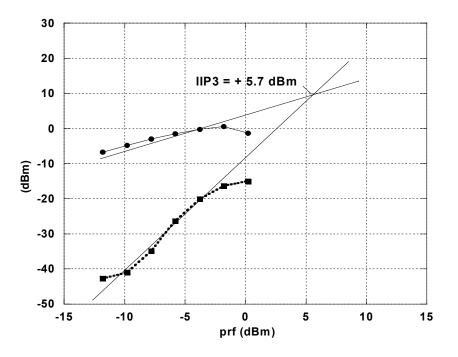

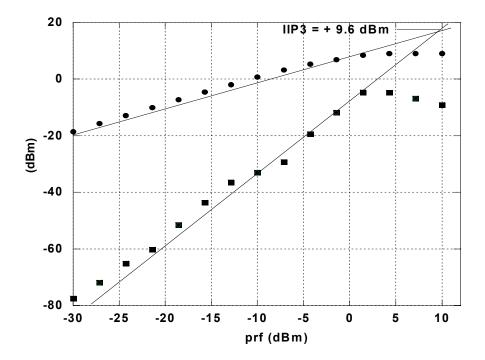

| <i>IIP3</i> of LNA2 with I <sub>dc</sub> =1mA                                | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

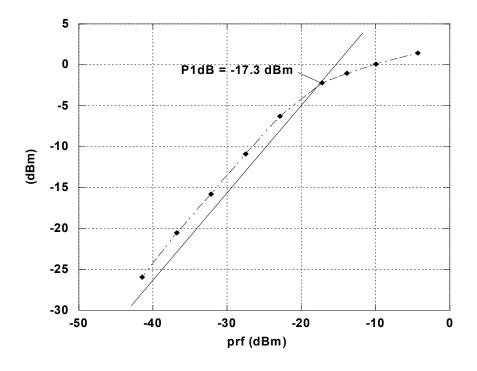

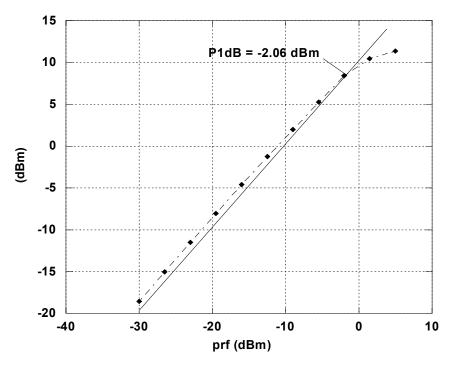

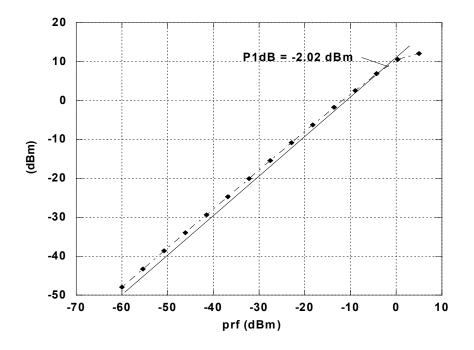

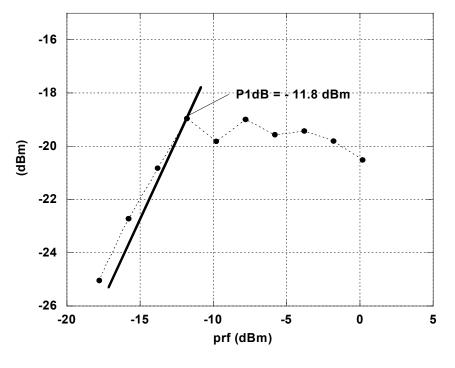

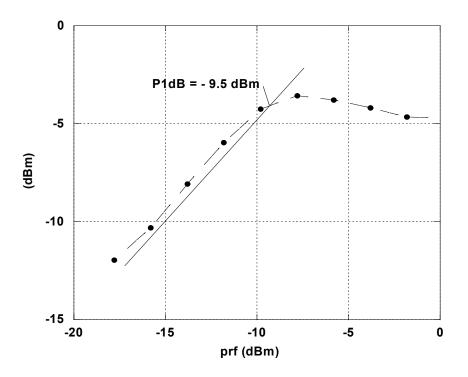

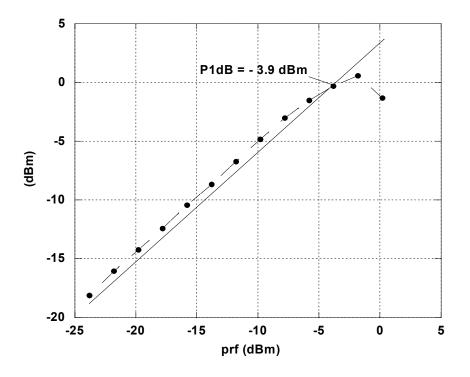

| <i>P1dB</i> of LNA5 with I <sub>dc</sub> =1mA                                | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

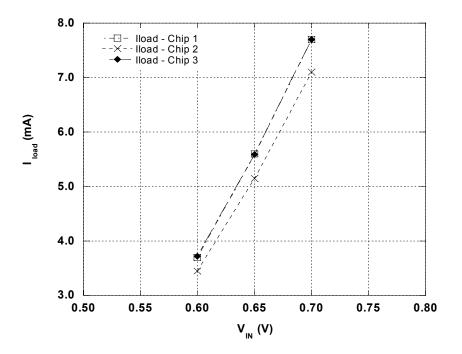

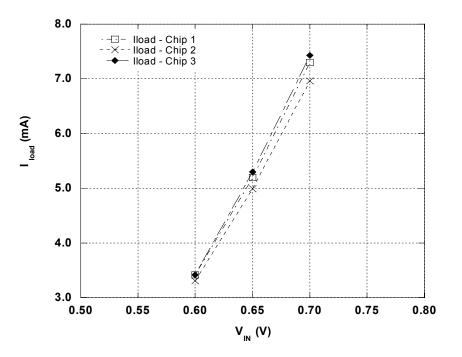

| Measured $I_{\text{load}}$ versus $V_{\text{IN}}$ (bias) for LNA4            | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

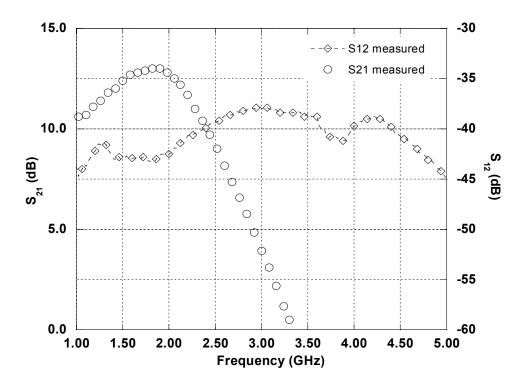

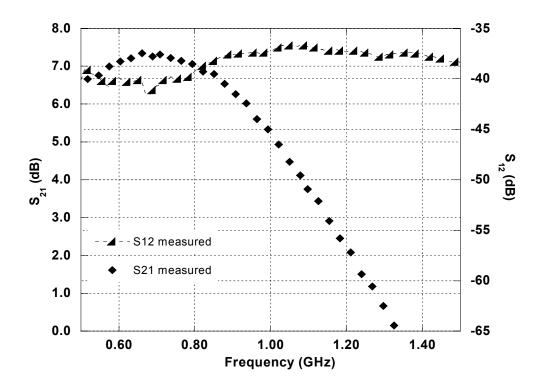

| Forward gain and reverse isolation of LNA4 with 0.7V bias                    | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Forward gain and reverse isolation of LNA4 with 0.65V bias                   | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Forward gain and reverse isolation of LNA4 with 0.6V bias                    | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

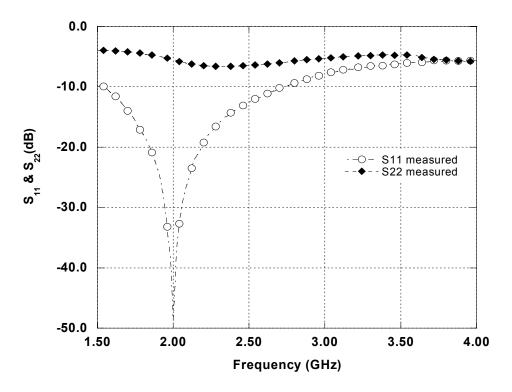

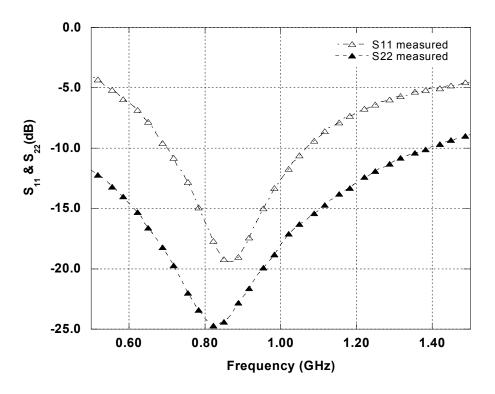

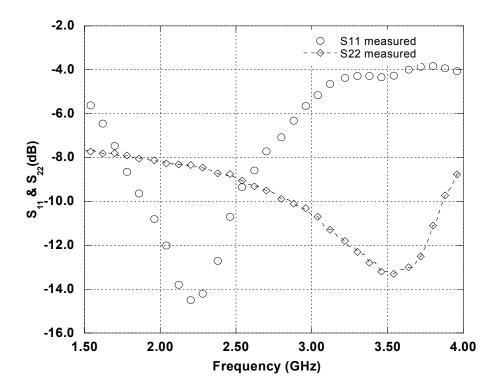

| Input and output return losses of the LNA4 with 0.7V bias                    | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input and output return losses of the LNA4 with 0.65V bias                   | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input and output return losses of the LNA4 with 0.6V bias                    | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

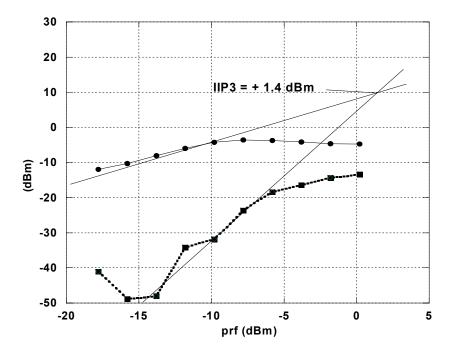

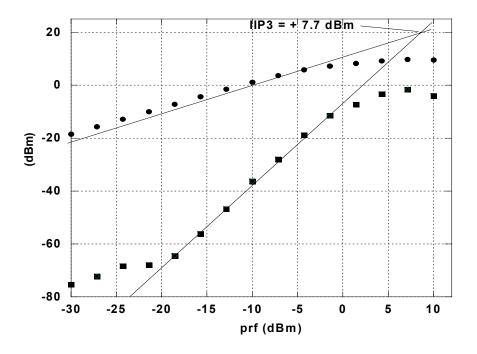

| <i>IIP3</i> of LNA4 with 0.7V bias                                           | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <i>P1dB</i> of LNA4 with 0.7V bias                                           | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Measured $I_{\text{load}}$ versus $V_{\text{IN}}$ (bias) for LNA5            | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                              | Output return loss ( $S_{22}$ ): fix $R_I$ but different values of $L_I$<br>Output return loss ( $S_{22}$ ): fix $L_I$ but different values of $R_I$<br>Measurement strategy [95]<br>Measured I <sub>load</sub> versus I <sub>dc</sub><br>Forward gain and reverse isolation of LNA2 with I <sub>dc</sub> =1mA<br>Forward gain and reverse isolation of LNA2 with I <sub>dc</sub> =5mA<br>Forward gain and reverse isolation of LNA2 with I <sub>dc</sub> =10mA<br>Input and output return losses of the LNA2 with I <sub>dc</sub> =1mA<br>Input and output return losses of the LNA2 with I <sub>dc</sub> =5mA<br>Input and output return losses of the LNA2 with I <sub>dc</sub> =10mA<br><i>IIP3</i> of LNA2 with I <sub>dc</sub> =1mA<br><i>PIdB</i> of LNA5 with I <sub>dc</sub> =1mA<br>Measured I <sub>load</sub> versus V <sub>IN</sub> (bias) for LNA4<br>Forward gain and reverse isolation of LNA4 with 0.7V bias<br>Forward gain and reverse isolation of LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias<br>Input and output return losses of the LNA4 with 0.65V bias |

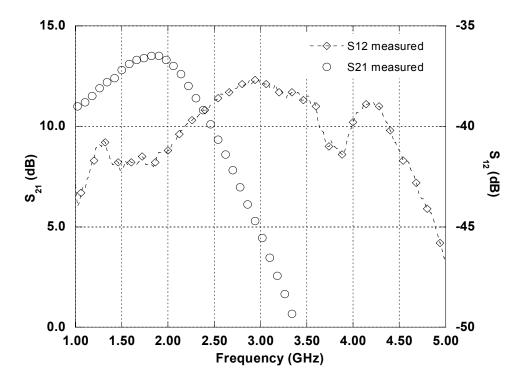

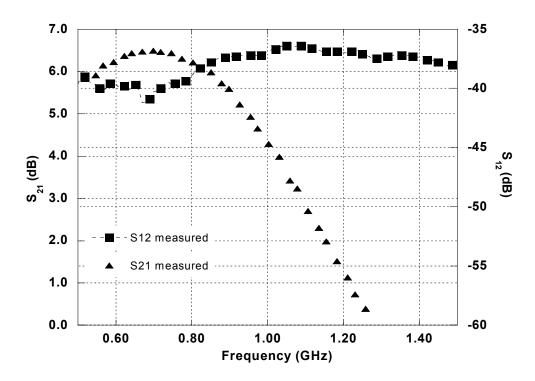

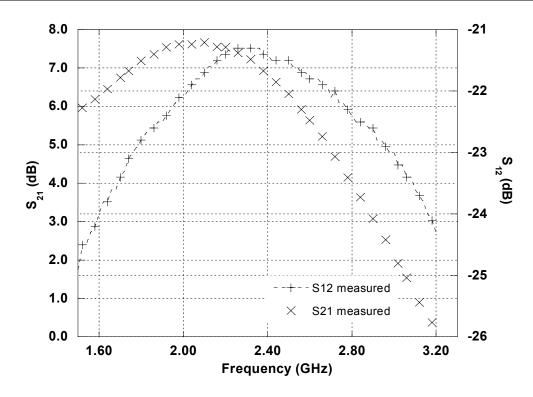

| Figure 5.21: | Forward gain and reverse isolation of LNA5 with 0.7V bias         | 142 |

|--------------|-------------------------------------------------------------------|-----|

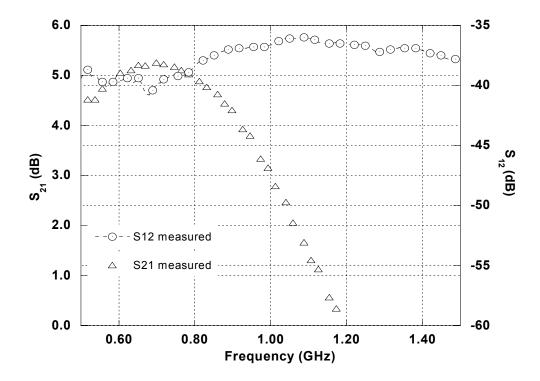

| Figure 5.22: | Forward gain and reverse isolation of LNA5 with 0.65V bias        | 143 |

| Figure 5.23: | Forward gain and reverse isolation of LNA5 with 0.6V bias         | 143 |

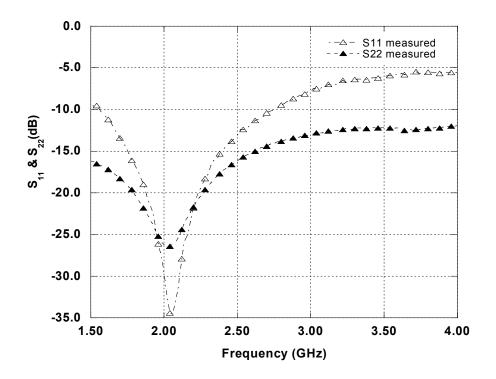

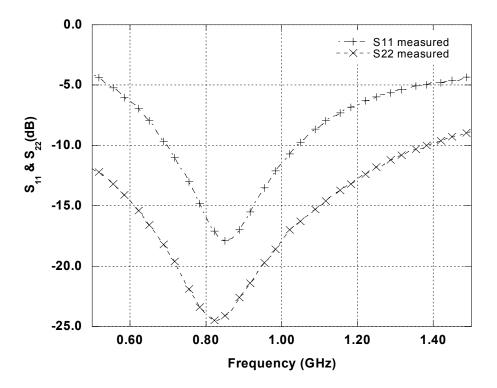

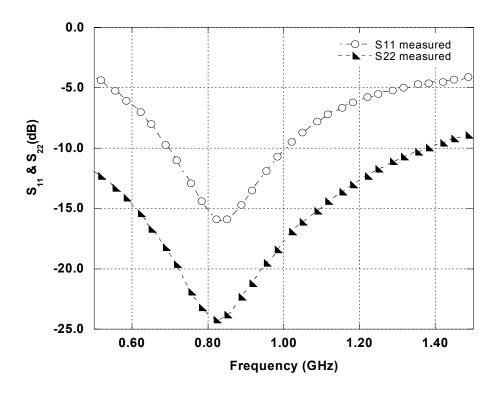

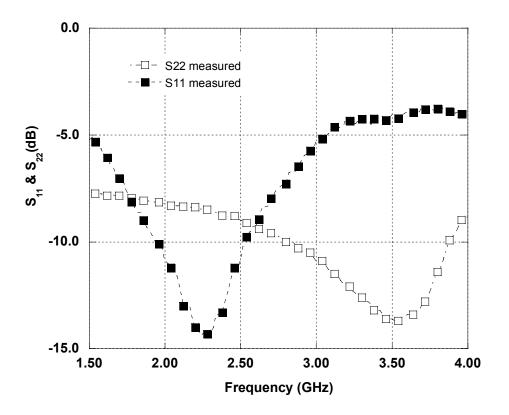

| Figure 5.24: | Input and output return losses of the LNA5 with 0.7V bias         | 144 |

| Figure 5.25: | Input and output return losses of the LNA5 with 0.65V bias        | 145 |

| Figure 5.26: | Input and output return losses of the LNA5 with 0.6V bias         | 146 |

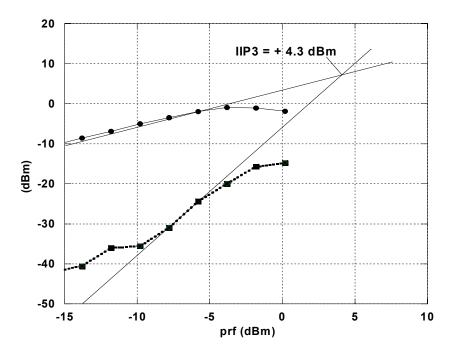

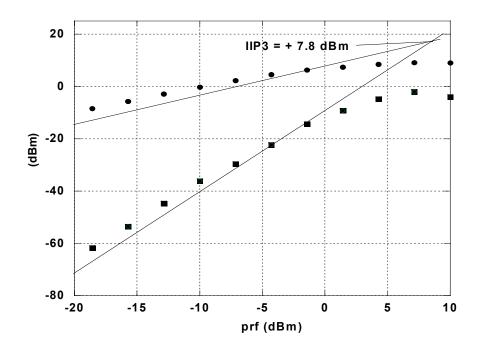

| Figure 5.27: | IIP3 of LNA5 with 0.7V bias                                       | 148 |

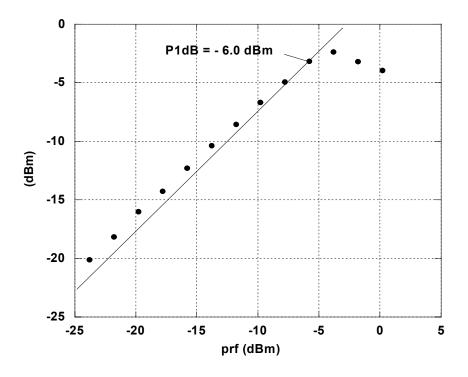

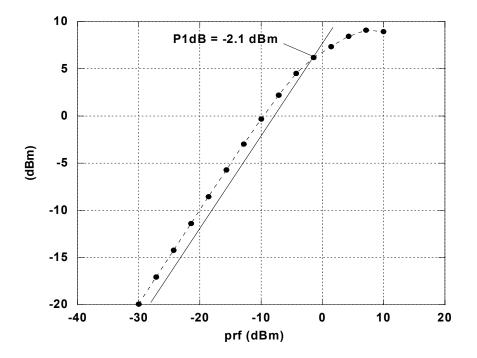

| Figure 5.28: | <i>P1dB</i> of LNA5 with 0.7V bias                                | 148 |

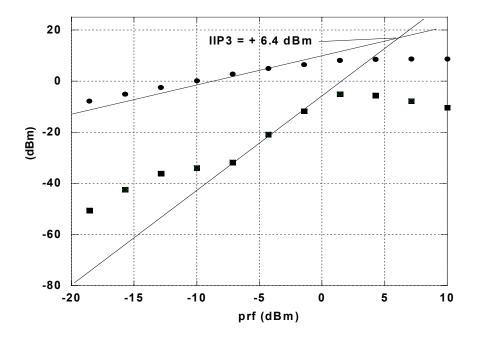

| Figure 5.29: | IIP3 of LNA5 with 0.65V bias                                      | 149 |

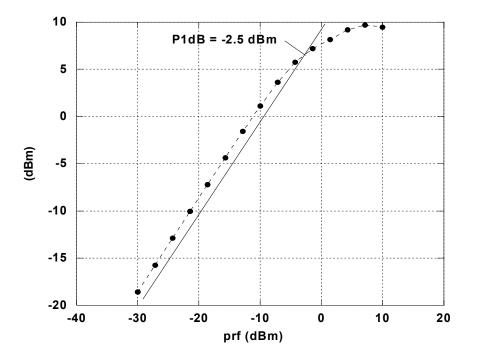

| Figure 5.30: | <i>P1dB</i> of LNA5 with 0.65V bias                               | 149 |

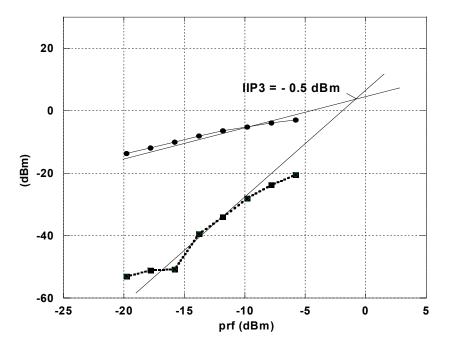

| Figure 5.31: | <i>IIP3</i> of LNA5 with 0.6V bias                                | 150 |

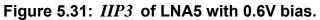

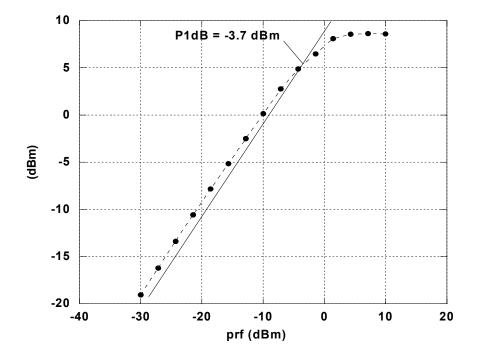

| Figure 5.32: | <i>P1dB</i> of LNA5 with 0.6V bias                                | 150 |

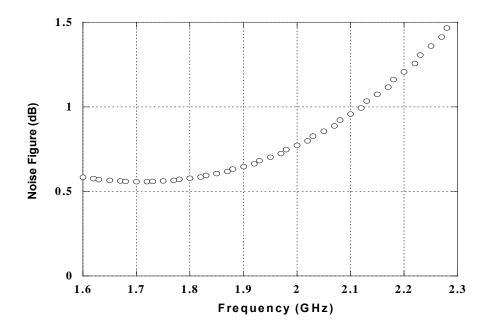

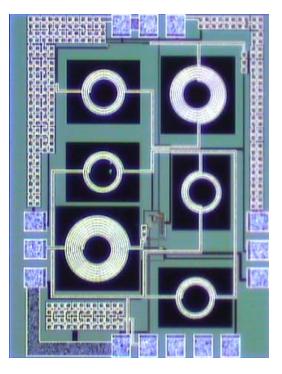

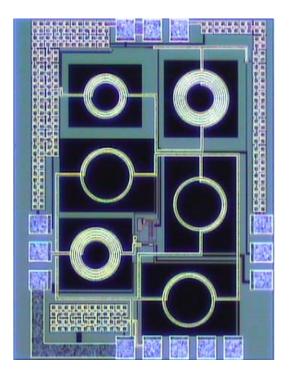

| Figure 5.33: | Die photograph of LNA2                                            | 151 |

| Figure 5.34: | Die photograph of LNA4                                            | 152 |

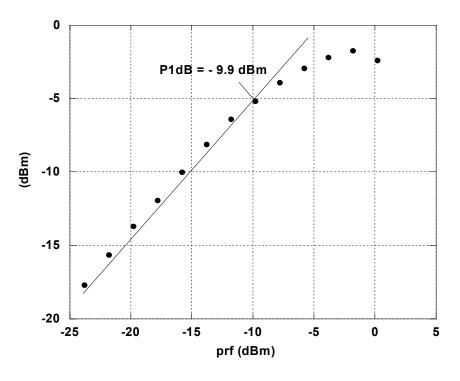

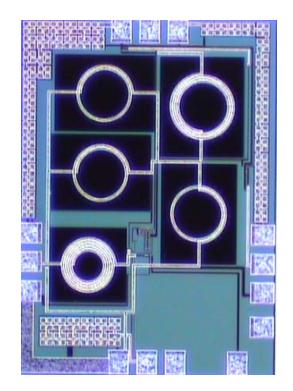

| Figure 5.35: | Die photograph of LNA5                                            | 152 |

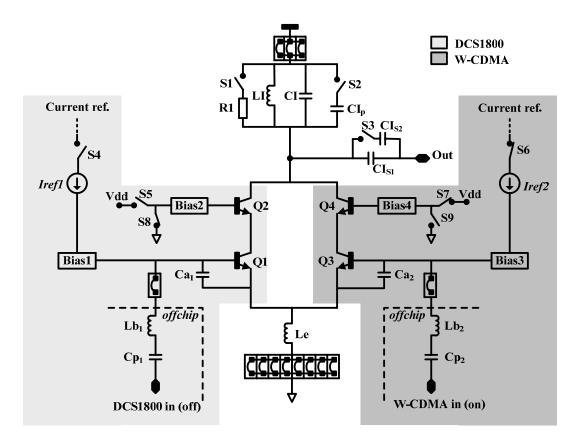

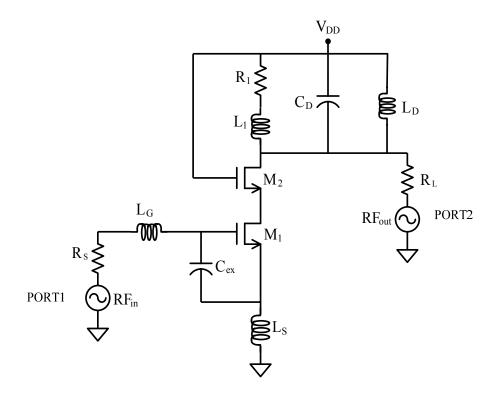

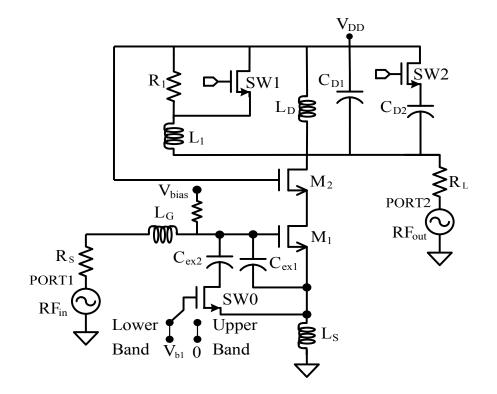

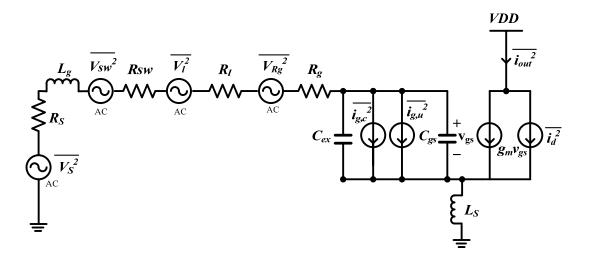

| Figure 6.1:  | Circuit diagram of a reconfigurable multi-standard multi-band LNA | 163 |

| Figure 6.2:  | Revised IDCS small-signal model for reconfigurable LNA            | 163 |

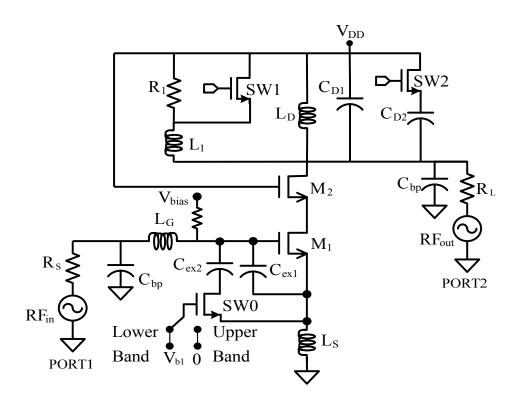

| Figure 6.3:  | Complete circuit implementation of a reconfigurable LNA           | 171 |

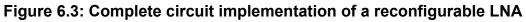

| Figure 6.4:  | Forward gain and reverse isolation of reconfigurable LNA          |     |

|              | for upper band at 2GHz                                            | 172 |

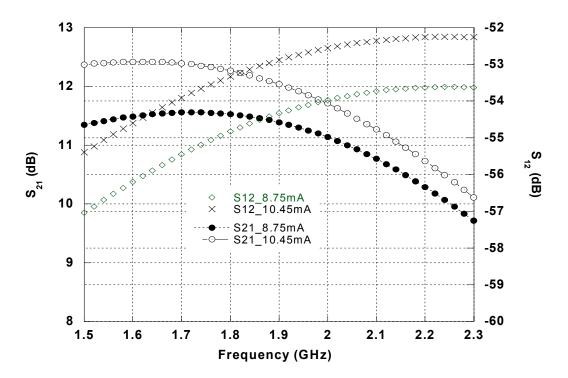

| Figure 6.5:  | Forward gain and reverse isolation of reconfigurable LNA          |     |

|              | for lower band at 0.9GHz                                          | 173 |

| Figure 6.6:  | Input and output return losses of reconfigurable LNA              |     |

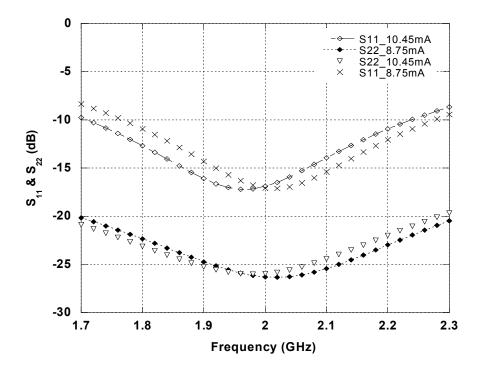

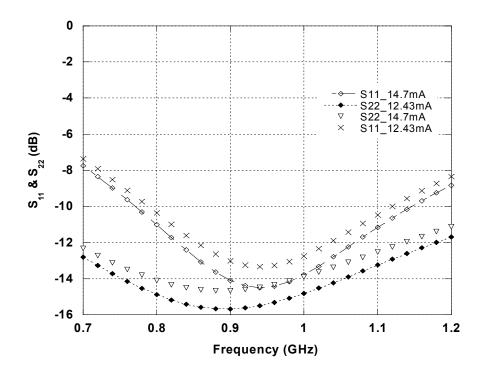

|              | for upper band at 2GHz                                                  | 174 |

|--------------|-------------------------------------------------------------------------|-----|

| Figure 6.7:  | Input and output return losses of reconfigurable LNA                    |     |

|              | for lower band at 0.9GHz                                                | 175 |

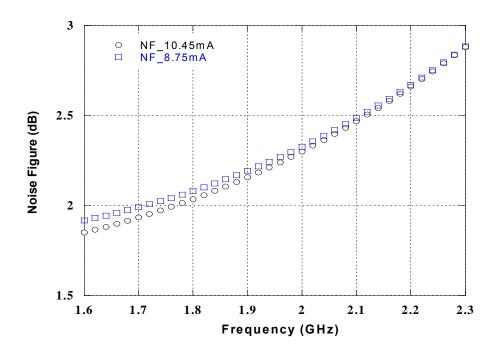

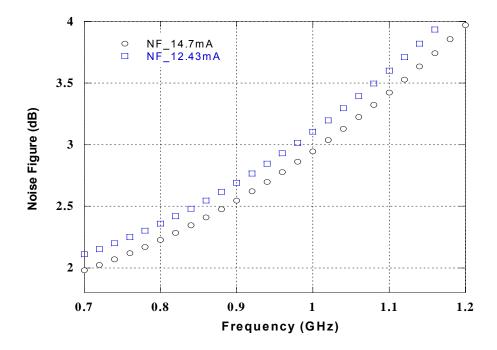

| Figure 6.8:  | Noise figure of reconfigurable LNA for upper band at 2 GHz              | 176 |

| Figure 6.9:  | Noise figure of reconfigurable LNA for lower band at 0.9 GHz            | 177 |

| Figure 6.10: | <i>IIP3</i> for upper band at 2 GHz with I <sub>load</sub> =10.45 mA    | 178 |

| Figure 6.11: | <i>IIP3</i> for upper band at 0.9 GHz with I <sub>load</sub> =14.7 mA   | 178 |

| Figure 6.12: | <i>IIP3</i> for upper band at 2 GHz with I <sub>load</sub> =8.75 mA     | 179 |

| Figure 6.13: | <i>IIP3</i> for upper band at 0.9 GHz with I <sub>load</sub> =12.43 mA  | 179 |

| Figure 6.14: | <b><i>P1dB</i></b> for upper band at 2 GHz with $I_{load}$ = 10.45 mA   | 180 |

| Figure 6.15: | <b><i>P1dB</i></b> for upper band at 0.9 GHz with $I_{load}$ = 14.7 mA  | 180 |

| Figure 6.16: | <b><i>P1dB</i></b> for upper band at 2 GHz with $I_{load}$ = 8.75 mA    | 181 |

| Figure 6.17: | <b><i>P1dB</i></b> for upper band at 0.9 GHz with $I_{load}$ = 12.43 mA | 181 |

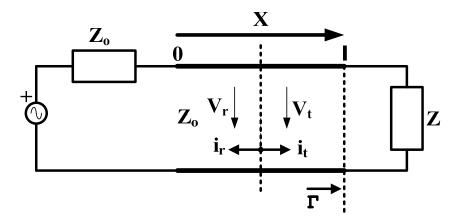

| Figure A.1:  | Transmitted and reflected voltages and currents [93]                    | 212 |

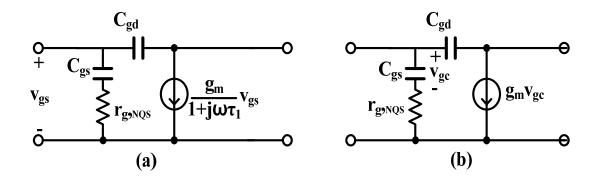

| Figure B.1:  | A first order non-quasi static small-signal model for transistors       |     |

|              | operating in strong inversion: (a) valid in both linear and             |     |

|              | saturation region (b) valid in saturation region only [93]              | 214 |

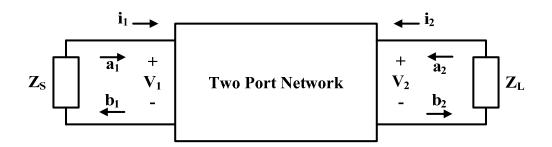

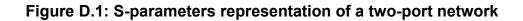

| Figure D.1:  | S-parameters representation of a two-port                               | 218 |

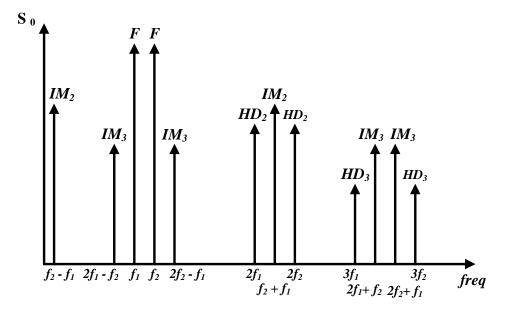

| Figure E.1:  | Frequency locations of distortion terms [104]                           | 223 |

|              |                                                                         |     |

## LIST OF TABLES

| Table 2.1: | Frequency allocation for GSM systems [2-4]                       | 16  |

|------------|------------------------------------------------------------------|-----|

| Table 2.2: | Frequency allocation for UMTS systems [7]                        | 16  |

| Table 2.3: | Signal characteristics for GSM/3G systems                        | 17  |

| Table 2.4: | Receiver specifications for GSM/3G systems and the proposed      |     |

|            | specifications for multi-standard system [46-48]                 | 19  |

| Table 2.5: | Ideal LNA specifications proposed for multi-standard             |     |

|            | multi-band system                                                | 20  |

| Table 2.6: | Typical LNA specifications proposed for multi-standard           |     |

|            | multi-band system                                                | 20  |

| Table 3.1: | Component values for LNA1                                        | 71  |

| Table 3.2: | Component values for LNA2                                        | 73  |

| Table 3.3: | Component values for LNA3                                        | 77  |

| Table 3.4: | Component values for LNA4                                        | 79  |

| Table 3.5: | Component values for LNA5                                        | 81  |

| Table 4.1: | Performance summary of the wide band LNAs                        | 116 |

| Table 5.1: | Performance summary of the measurement results for               |     |

|            | chip 2 of the LNA2                                               | 129 |

| Table 5.2: | Performance summary of the measurement results for               |     |

|            | chip 3 of the LNA2                                               | 130 |

| Table 5.3: | Linearity performance summary of the other current bias for LNA2 | 132 |

| Table 5.4: | Performance summary of the measurement results for               |     |

|            | chip 2 of the LNA4                                               | 138 |

|            |                                                                  |     |

| Table 5.5:  | Performance summary of the measurement results for                |     |

|-------------|-------------------------------------------------------------------|-----|

|             | chip 3 of the LNA4                                                | 139 |

| Table 5.6:  | Linearity performance summary of the other chip for LNA4          | 140 |

| Table 5.7:  | Performance summary of the measurement results for                |     |

|             | chip 2 of the LNA5                                                | 146 |

| Table 5.8:  | Performance summary of the measurement results for                |     |

|             | chip 3 of the LNA5                                                | 147 |

| Table 5.9:  | Linearity performance summary of the other chips for LNA5         | 151 |

| Table 5.10: | Performance summary of the wide band LNAs                         | 155 |

| Table 5.11: | Achieved bandwidths of the wide band LNAs                         | 156 |

| Table 5.12: | Comparison with other publications                                | 157 |

| Table 6.1:  | Component values for reconfigurable multi-standard multi-band LNA | 171 |

| Table 6.2:  | Performance summary of the reconfigurable LNA                     |     |

|             | versus wide band LNAs                                             | 183 |

| Table AC.1: | Performance summary of the inductors                              | 217 |

## LIST OF PUBLICATIONS

#### Journals

Mustaffa M.T, Zayegh A, Veljanovski R., Stojcevski A., and Zulkifli T.Z.A., "CMOS Low Noise Amplifier for wideband mobile receiver," Accepted for publication in Journal of the Advancement of Modelling and Simulation Techniques (AMSE), France, in 2008.

#### **Conference papers**

- Mustaffa M.T, Zayegh A, Veljanovski R., Stojcevski A., and Zulkifli T.Z.A., "0.18 µm Fully Integrated 900 MHz CMOS LNA with Input and Output On-chip matching for Multi-standard Mobile Receiver," Proceedings of IEEE International Conference on Microelectronics, 14-17 December 2008, Sharjah, UAE.

- Mustaffa M.T, Zayegh A, Veljanovski R., Stojcevski A., and Zulkifli T.Z.A., "Fully Integrated 2-GHz LNA with On-chip matching for Multi-standard Mobile Receiver using 0.18 µm CMOS Technology," Proceedings of IEEE TENCON International Conference, 18-21 November 2008, Hyderabad, India.

- Mustaffa M.T, Zayegh A, Veljanovski R. and Stojcevski A., "A 0.8 GHz to 1 GHz 0.25 µm CMOS Low Noise Amplifier for Multi-standard Receiver," Proceedings of IEEE International Conference on Intelligent & Advanced Systems, 25-28 November 2007, Kuala Lumpur, Malaysia.

- Mustaffa M.T, Zayegh A, Veljanovski R. and Stojcevski A., "A 1.8 GHz to 2.1 GHz 0.25 µm CMOS Wideband LNA for a Multi-standard Mobile Receiver," Proceedings of IEEE International Symposium on Integrated Circuits (ISIC), 26-28 September 2007, Orchard Hotel, Singapore.

- Mustaffa M.T, Zayegh A, Veljanovski R. and Stojcevski A., "Optimised Low Noise Amplifier for Multi-standard Receiver Architecture," Proceedings of International Conference on Advanced Technologies in Telecommunications and Control Engineering (ATTCE), 28-29 August 2006, INTI College, Malaysia.

## **CHAPTER 1:**

## **THESIS OVERVIEW**

## 1.0 Introduction

The increasing demands of higher data transfer rates and global mobility in current wireless communication environment has led to the development of the Third Generation (3G) mobile communication standard. Nowadays, many small and large operators, serving both developed and emerging markets, are already reaping the benefits of 3G technologies. As of January 2008, there were 435 3G operators (service providers) worldwide, with more than 560 million subscribers in 143 countries [1].

The 3G wireless communication system provides voice communication together with multimedia communication such as video, internet, real TV, live cast, etc. as is represented in Figure 1.1. It supports Universal Mobile Telecommunication System (UMTS) or Wide Code Division Multiple Access (WCDMA) standard and also provides a backward compatibility with Second Generation (2G) systems [2-9]. Typical standards currently being used for 2G systems are: Global Standard for Mobile (GSM900) and Digital Cellular System (DCS1800) and Personal Communication System (PCS1900) [2-9]. In other words, the new 3G phone is a representation of new wireless trend toward the integration of multiple standards multiple functions into one wireless device that is targeted to be used virtually anywhere in the world.

Figure 1.1: 3G phone with various applications [1]

Due to increasing demand on the 3G mobile, QUALCOMM, Texas Instrument (TI), etc. (companies that provide chipset solution for 3G systems) have come up with systems using parallel architecture to cover various standards [10-12]. This concept of parallel architecture maybe originated from various radio frequency (RF) multi-standard multi-band parallel systems which were developed over the past years as shown in references [13-20]. Unfortunately, this type of implementation is very area inefficient, costly and consumes relatively high power due to the fact that different standards need

different systems or devices. In other words, consumers are paying additional cost for the added complexity of such a system. In addition, with the complex functionality (email, video call, etc.), the issue of a shorter battery life of a 3G phone compared to wellknown GSM mobile is quite common, as the battery might go flat within just one day, or even worse, within hours if heavy usage of the 3G mobile took place.

Having mentioned the problems with the current solutions, it is impractical in the future to adapt such implementation in designing the multi-standard multi-band mobile device, as more and more 3G wireless standards are emerging [8-9]. With these emerging standards, wireless mobile system is more complex and the system integration is virtually impossible or hard to be realised and impractical. Therefore, the search for a new system or architecture seems to be evident. Solutions to these problems are possible by introducing a new architecture with reconfigurability features that should be able to support most of the available standards [8-9].

With respect to this approach, it is possible to develop a new architecture that can cover various standards with just one single terminal, compared to the current architecture that uses a single terminal for each single standard. For instance, as GSM comprise standards that use multiple bands in the lower frequency bands: 850 and 900 MHz and the upper frequency bands: 1800 and 1900 MHz [2-9], two new circuits (in particular, low noise amplifier (LNA) as it is the main work of this research) could be designed to support these lower and upper frequency band regimes.

For the reconfigurability feature, the principle refers to the ability of the circuit to perform changes in function due to the operating environment by selecting certain section of the circuit at one time to operate, while the other sections can be switched off to reduce power consumption. Referring to this research work, reconfigurable means to modify the hardware structure to respond to the two major bands of interest (i.e. lower and upper frequency band regimes) depending on the availability of the mobile communication systems (GSM or 3G).

To design such a new architecture with reconfigurability feature, a platform (i.e. mobile receiver system) is required. Since LNA is part of the receiver system, a good receiver architecture that is suitable for multi-standard multi-band implementation is needed. From the literature, direct conversion receiver (DCR) architecture is believed to be the most suitable architecture for single-chip multi-standard multi-band mobile receiver [18-19]. This is because of its advantages such as simple circuit architecture and less off-chip components, leading to low power consumption with possible integration as a single-chip radio [18-24].

In DCR architecture, RF signal is amplified and converted to baseband signal in only one stage. Typically, DCR architecture consists of a Band Pass Filter (BPF), a LNA, a mixer, a voltage controlled oscillator (VCO), etc. In DCR architecture, LNA is considered as the most important block, as it directly affects the performance of the receiver. It amplifies the RF signal to a sufficient power level required for the subsequent stages to process the signal and at the same time offers low noise figure (NF) and high linearity to increase the accuracy and performance of the system.

For years, LNA has been the topic of research due to its different performance requirements for different standards [25-33]. Gain, NF, linearity, and low power consumption are the major specifications in the design of LNA, and the most important parameter is NF. To achieve a low NF, common source stage with inductive degeneration showed the best noise performance with good gain and sufficient linearity with a trade-off with power consumption [25-27]. Several techniques and methods have been tried in order to produce a LNA with low NF [25-33], but, most of these methods and techniques are limited to the single standards only.