VUS1/Z VU0001508

FOR LOAN

LC:

#### DATE DUE

🎽 • 👘 🔹

THE/ 1988/2 Box THE 00002

×

BRN: 380723

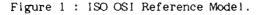

## A Local Area Network Using Spread Spectrum Techniques

A Thesis submitted for examination for the Degree of Master of Engineering (Electrical)

> By A. L. Simcock BSc(Hons)(Electronics) University of Kent at Canterbury, Canterbury. England.

Department of Electrical and Electronic Engineering, Footscray Institute of Technology, Victoria, Australia. December, 1988

## **Table of Contents**

1

2

| Tab  | le of Contents                                      | i    |

|------|-----------------------------------------------------|------|

| List | of Figures                                          | vii  |

| List | of Tables                                           | xi   |

| Ack  | nowledgements                                       | xii  |

| Abs  | tract                                               | xiii |

|      |                                                     |      |

| INT  | RODUCTION                                           | 1    |

| 1.1  | Summary                                             | 1    |

| 1.2  | The Emergence of Local Area Networks                | 2    |

| 1.3  | Spread Spectrum in LANs                             | 3    |

| 1.4  | Literature Survey and Existing Systems              | 5    |

|      | 1.4.1 System A                                      | 5    |

|      | 1.4.2 System B                                      | 6    |

|      | 1.4.3 System C                                      | 7    |

|      | 1.4.4 System D                                      | 7    |

| 1.5  | Autocorrelation, Crosscorrelation and Orthogonality | 8    |

| 1.6  | Features Required in CDMA Codes                     | 10   |

| 1.7  | Maximal Length Sequences                            | 11   |

| 1.8  | Basic Spread Spectrum Theory                        | 13   |

| 1.9  | Multiple Access in a Spread Spectrum System         | 19   |

|      |                                                     |      |

| OUT  | ILINE OF THE RESEARCH                               | 23   |

| 2.1  | Summary                                             | 23   |

| 2.2  | Design Aims                                         | 23   |

| 2.3  | Spread Spectrum vs Current Networks                 | 24   |

| 2.4  | System Specifications                               | 25   |

|      |                                                     |      |

i

| 3 | CODE | ES IN A C | DMA SYSTEM                                               | 29 |

|---|------|-----------|----------------------------------------------------------|----|

|   | 3.1  | Summ      | ary                                                      | 29 |

|   | 3.2  | Coding    | g Scheme Selection                                       | 29 |

|   |      | 3.2.1     | Scheme A - Segments of Long m-sequences                  | 30 |

|   |      | 3.2.2     | Scheme B - Different m-sequences of the Same Length      | 30 |

|   |      | 3.2.3     | Scheme C - Gold Codes                                    | 31 |

|   |      | 3.2.4     | Scheme D - Phase Shifted Versions of a Single m-sequence | 32 |

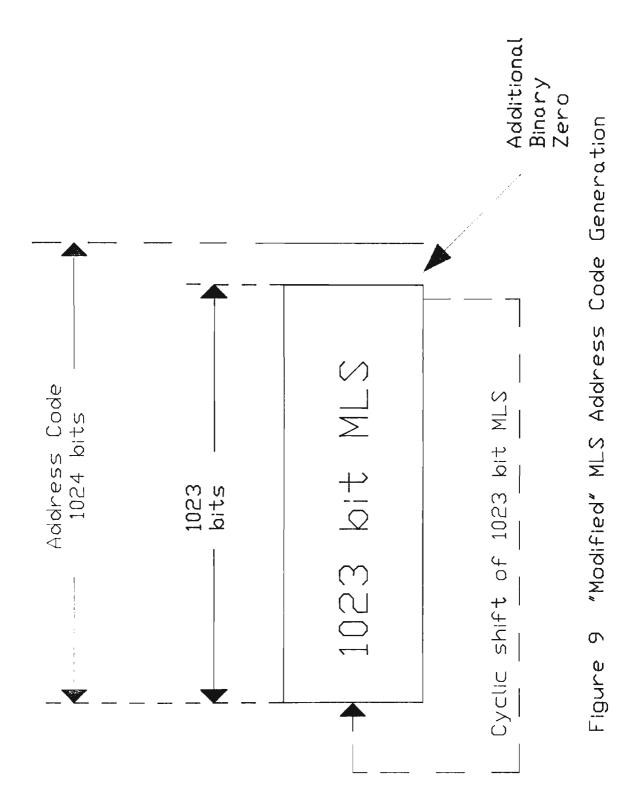

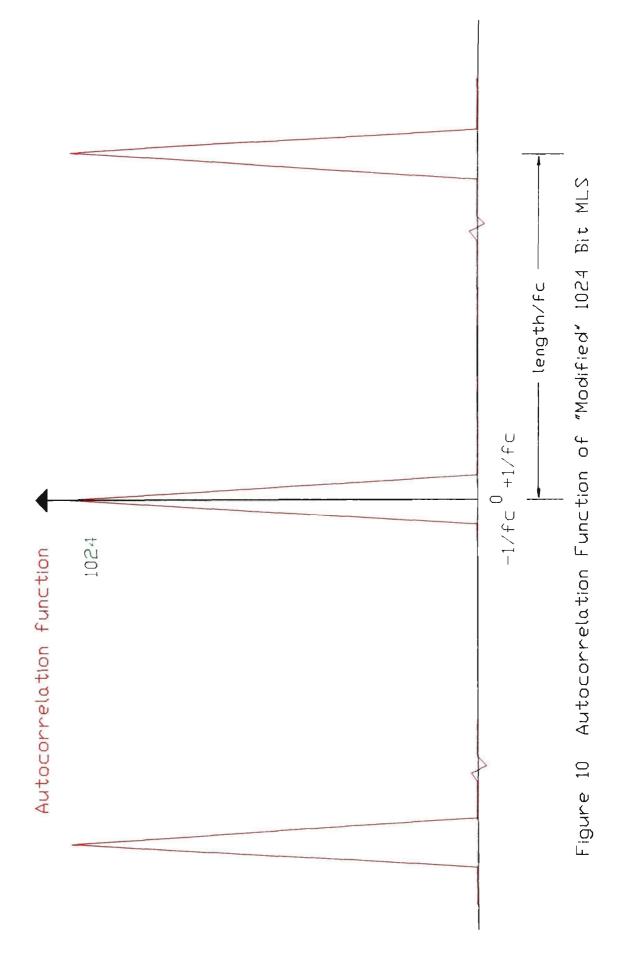

|   |      | 3.2.5     | Scheme F - Modified Maximal Length Sequences             | 34 |

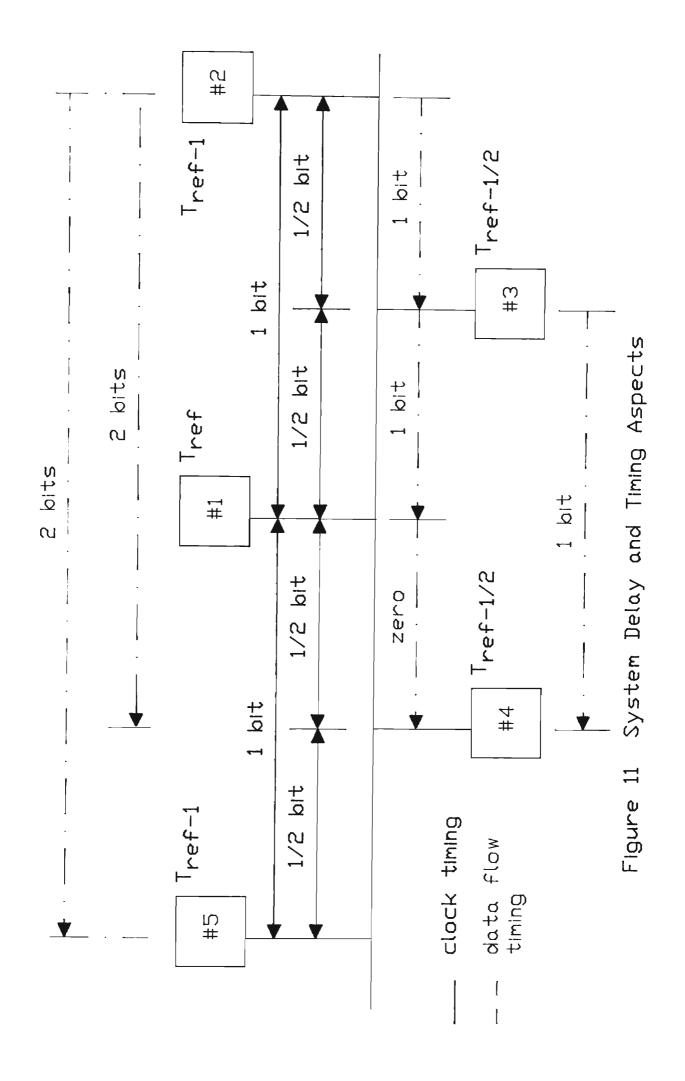

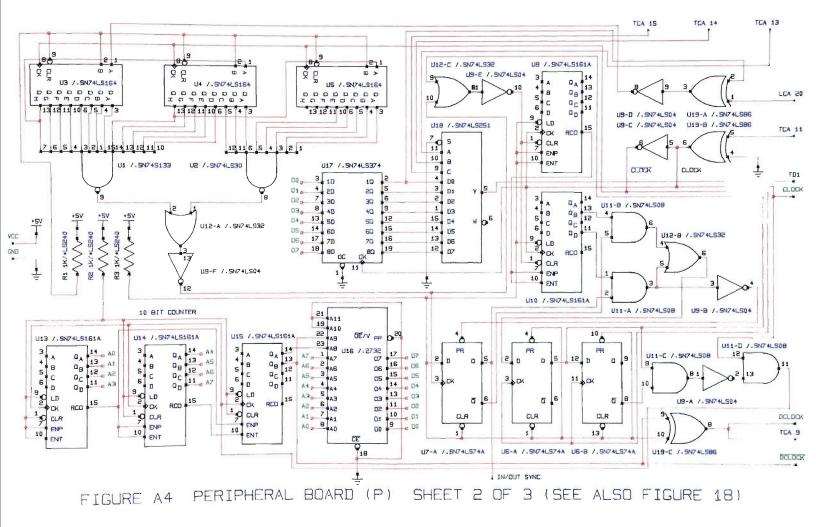

|   | 3.3  | System    | n Timing Concepts                                        | 37 |

|   | 3.4  | Sliding   | Correlator                                               | 41 |

|   | 3.5  | Collisio  | on Mechanisms and Characteristics                        | 42 |

|   |      |           |                                                          |    |

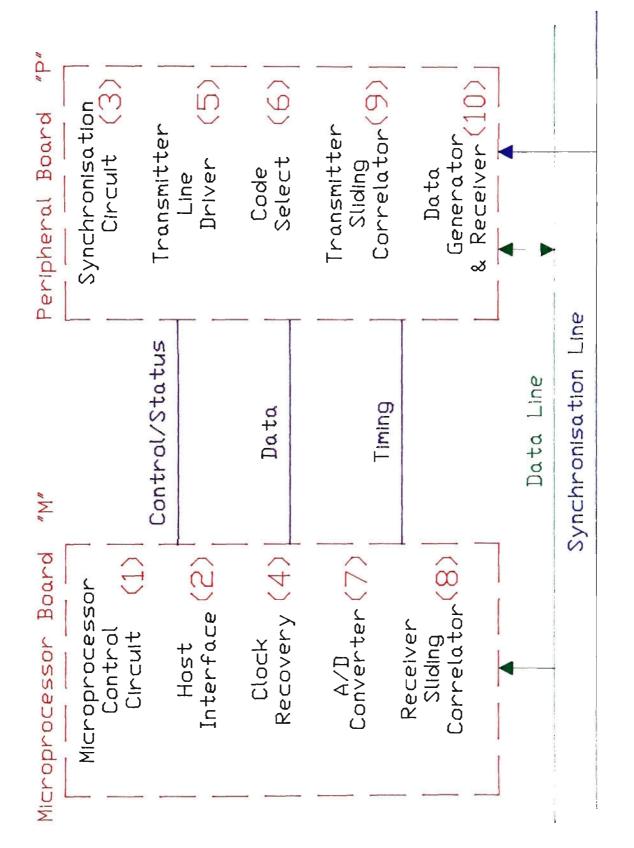

| 4 | HARE | OWARE     |                                                          | 43 |

|   | 4.1  | Summ      | ary                                                      | 43 |

|   | 4.2  | Overvi    | ew of Development Requirements                           | 43 |

|   | 4.3  | Brief O   | verview of Hardware                                      | 44 |

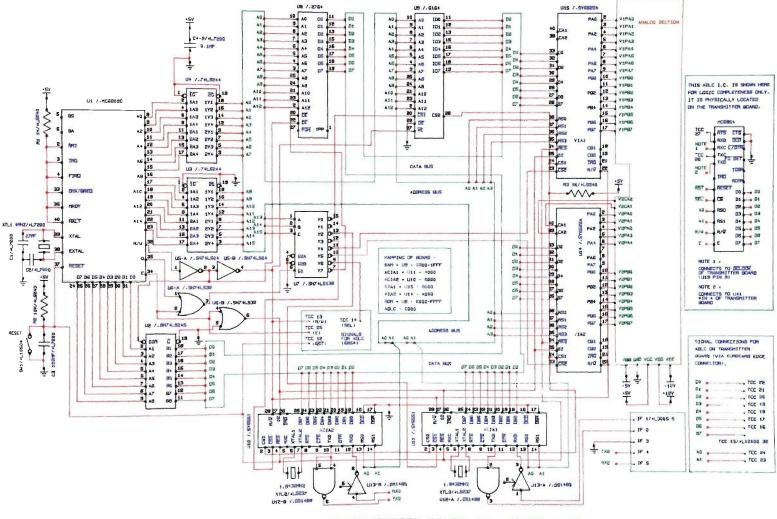

|   |      | 4.3.1     | Microprocessor Control Circuit - Board M                 | 44 |

|   |      | 4.3.2     | Host Interface - Board M                                 | 48 |

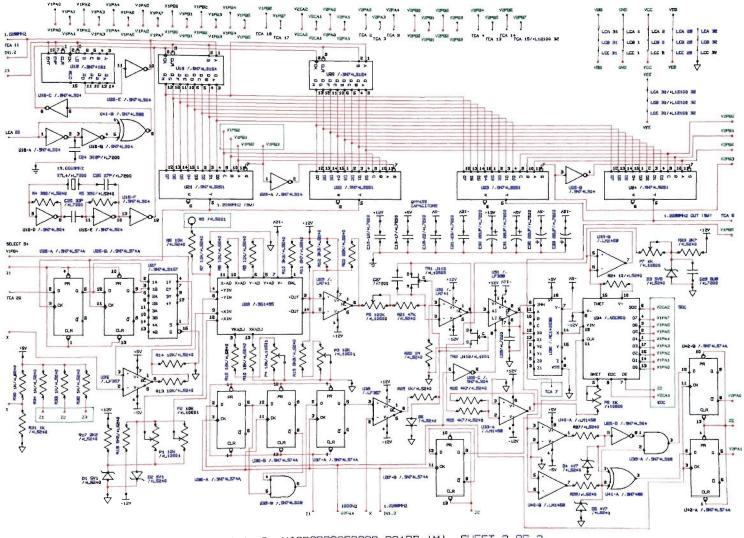

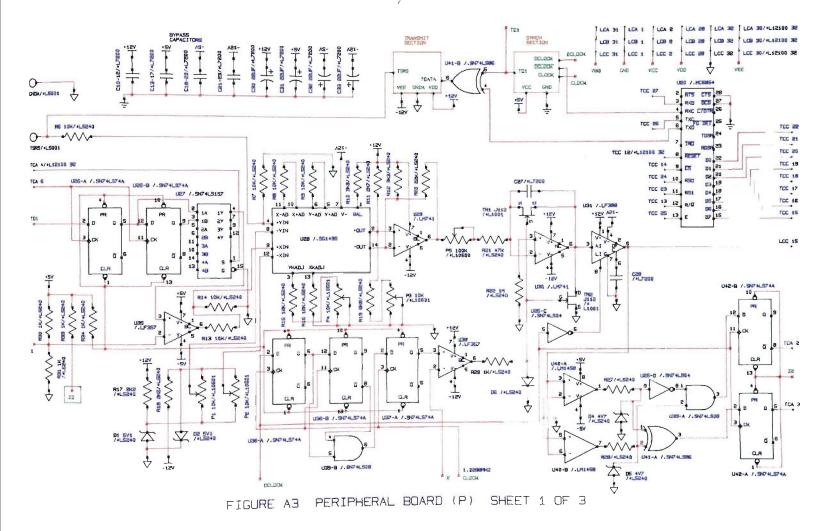

|   |      | 4.3.3     | Synchronisation Circuit - Board P                        | 48 |

|   |      | 4.3.4     | Clock Recovery - Board M                                 | 48 |

|   |      | 4.3.5     | Transmitter Line Driver - Board P                        | 48 |

|   |      | 4.3.6     | Code Select - Board P                                    | 49 |

|   |      | 4.3.7     | A/D Converter - Board M                                  | 49 |

|   |      | 4.3.8     | Receiver Sliding Correlator and Demodulator - Board M    | 49 |

|   |      | 4.3.9     | Transmitter Sliding Correlator and Demodulator - Board P | 50 |

|   |      | 4.3.10    | Data Generator/Receiver - Board P                        | 50 |

|   | 4.4  | Detaile   | d Hardware Description                                   | 50 |

|   |      | 4.4.1     | Microprocessor Control Circuit                           | 50 |

|   |      | 4.4.2     | Host Interface                                           | 52 |

|   |      | 4.4.3     | Synchronisation Circuits                                 | 52 |

|   |      |          | 4.4.3.1 Performance Tests on the Sync Circuit                          | 61         |

|---|------|----------|------------------------------------------------------------------------|------------|

|   |      | 4.4.4    | Clock Recovery                                                         | 63         |

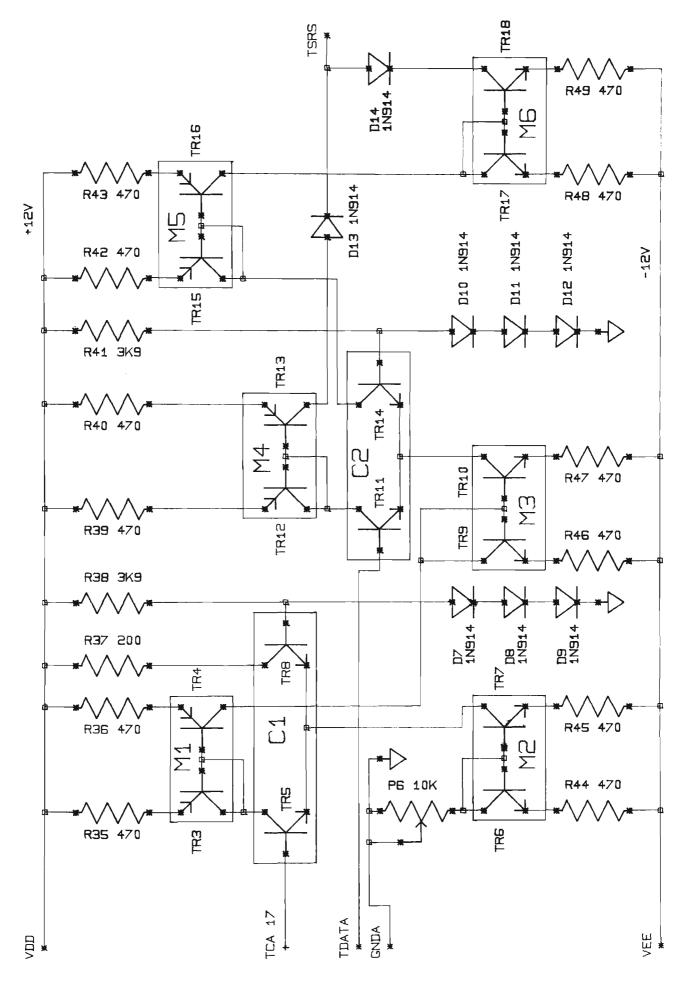

|   |      | 4.4.5    | Transmitter Line Driver                                                | 67         |

|   |      | 4.4.6    | Code Select                                                            | 72         |

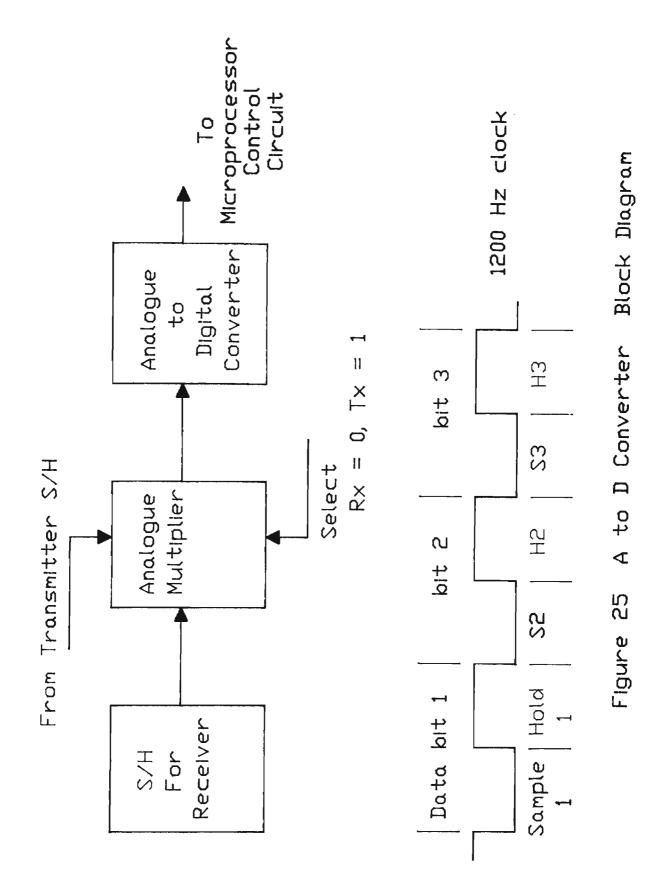

|   |      | 4.4.7    | Analogue to Digital Converter (ADC)                                    | 72         |

|   |      | 4.4.8    | Receiver                                                               | 74         |

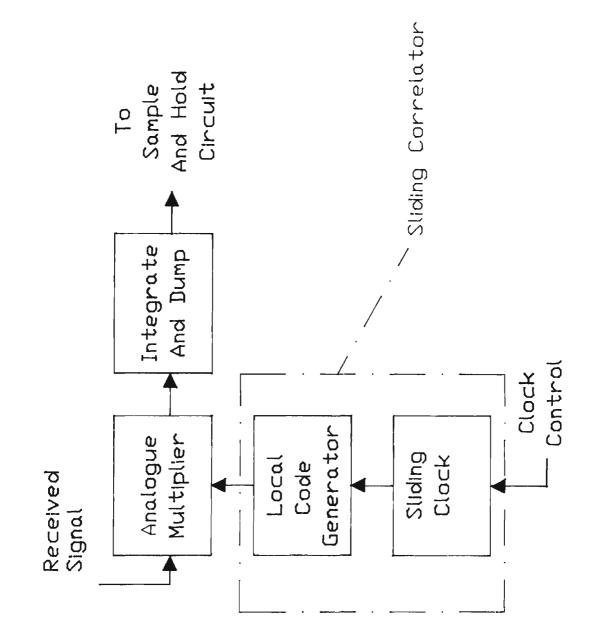

|   |      |          | 4.4.8.1 The Sliding Correlator                                         | 74         |

|   |      |          | 4.4.8.2 The Analogue Multiplier                                        | 76         |

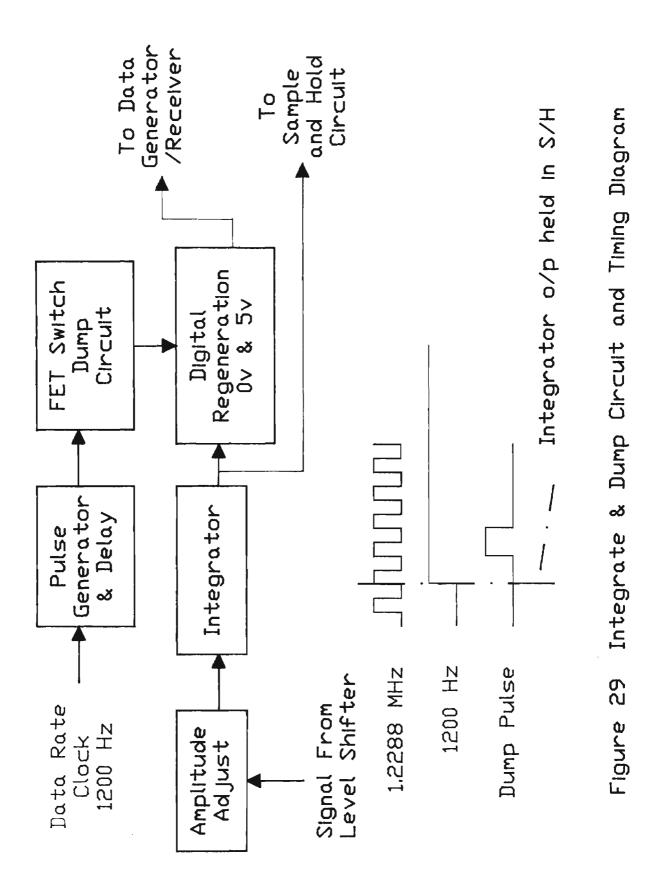

|   |      |          | 4.4.8.3 Integrate and Dump                                             | 79         |

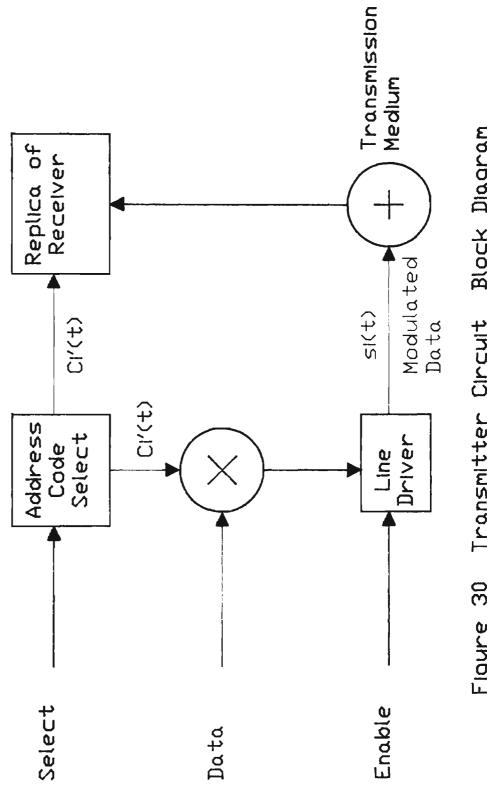

|   |      | 4.4.9    | Transmitter                                                            | 79         |

|   |      | 4.4.10   | Data Generator/Receiver                                                | 81         |

| 5 | HARD | WARE FL  | UNCTIONAL TESTING                                                      | 83         |

|   | 5.1  | Summa    | ary                                                                    | 83         |

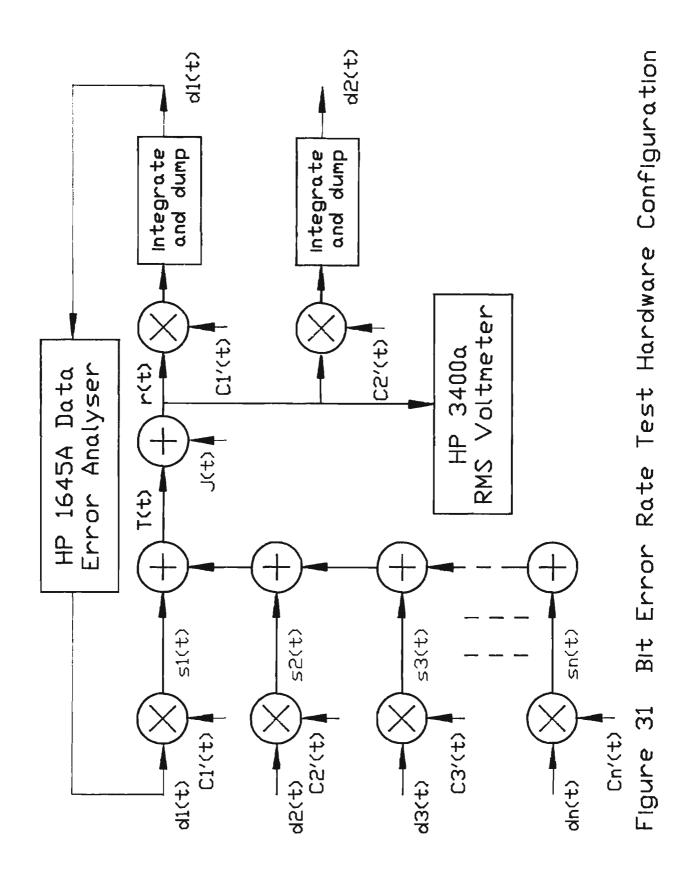

|   | 5.2  | Bit Erro | or Rate (BER) Test                                                     | 83         |

|   | 5.3  | Sliding  | Correlator Test                                                        | <b>8</b> 9 |

|   | 5.4  | Collisio | on Detection Tests                                                     | 91         |

|   |      | 5.4.1    | Test 1 Additive interference (overlap $\leq$ 1 bit)                    | 91         |

|   |      | 5.4.2    | Test 2 Additive interference ( 1 bit $\leq$ overlap $\leq$ 2 bits )    | 93         |

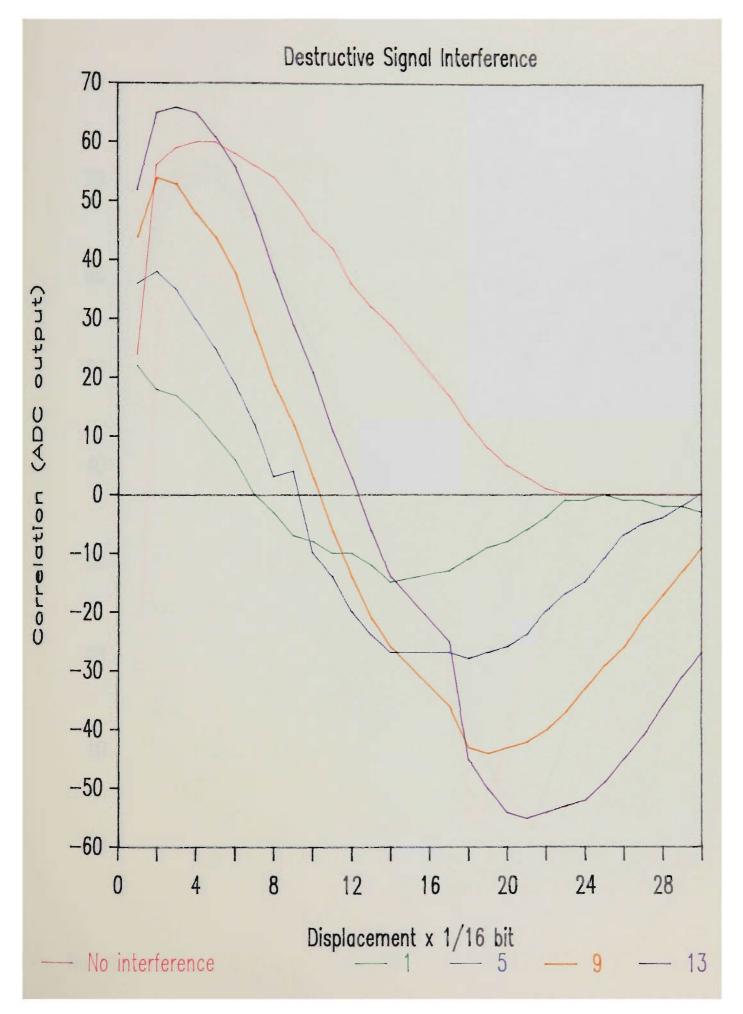

|   |      | 5.4.3    | Test 3 Destructive interference ( overlap $\leq$ 1 bit )               | 93         |

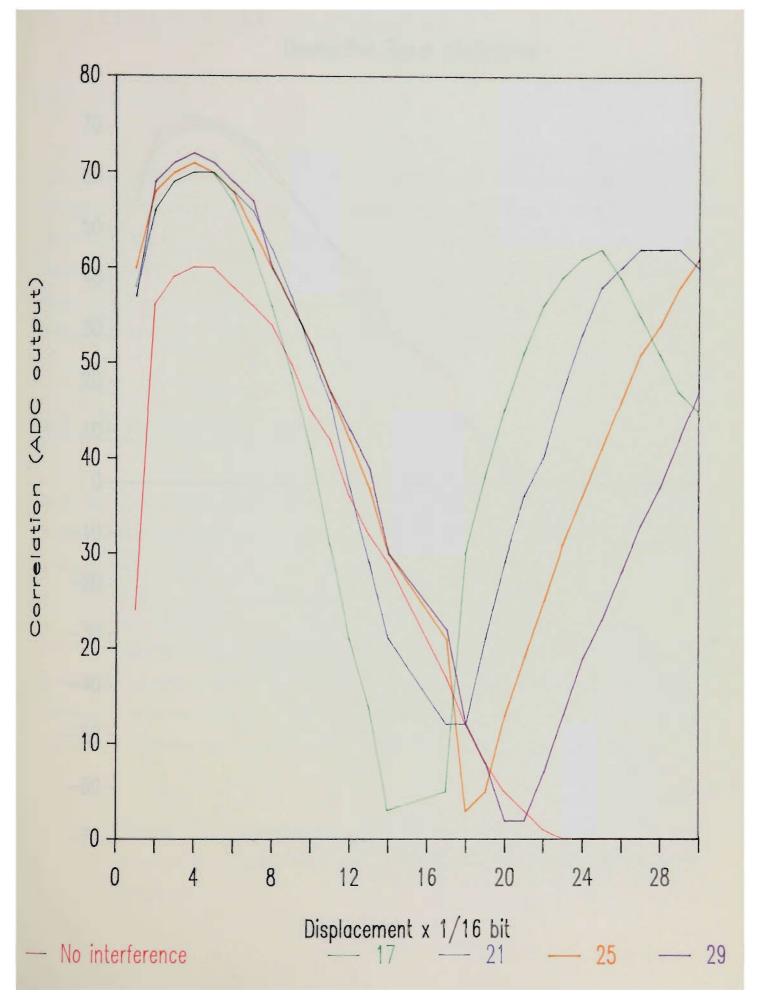

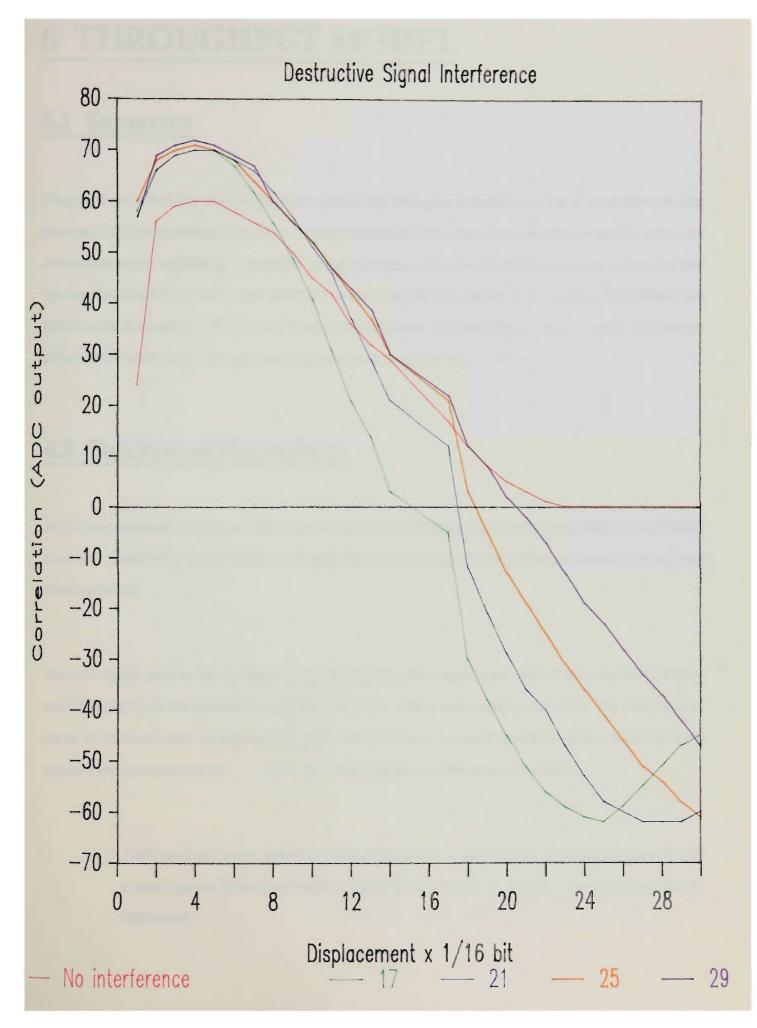

|   |      | 5.4.4    | Test 4 Destructive interference ( 1 bit $\leq$ overlap $\leq$ 2 bits ) | 96         |

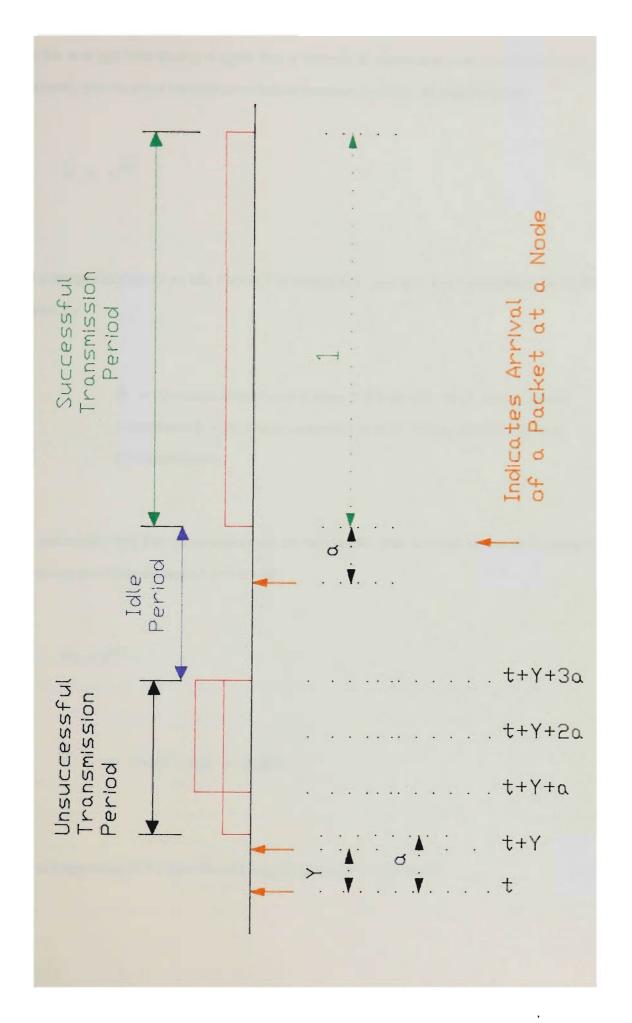

| 6 | THRO | UGHPUT   | T MODEL                                                                | 101        |

|   | 6.1  | Summ     | ary                                                                    | 101        |

|   | 6.2  | Theore   | etical Throughput                                                      | 101        |

|   | 6.3  | Simula   | tion of Throughput                                                     | 110        |

| 7 | SOFT |          | ND SYSTEM TESTING                                                      | 116        |

|   | 7.1  | Summa    | ary                                                                    | 116        |

|   | 7.2  | Overvie  | ew of Control Software                                                 | 116        |

|   |      |          |                                                                        |            |

|     | 7.3     | Contro   | ol of the Spread Spectrum Interface                       | 117 |

|-----|---------|----------|-----------------------------------------------------------|-----|

|     |         | 7.3.1    | Inputs                                                    | 117 |

|     |         | 7.3.2    | Outputs                                                   | 118 |

|     | 7.4     | ADLC     | Control                                                   | 120 |

|     |         | 7.4.1    | Receiver Control                                          | 121 |

|     |         | 7.4.2    | Transmitter Control                                       | 122 |

|     | 7.5     | Conne    | ction Testing                                             | 122 |

|     | 7.6     | Throug   | ghput Performance Testing                                 | 124 |

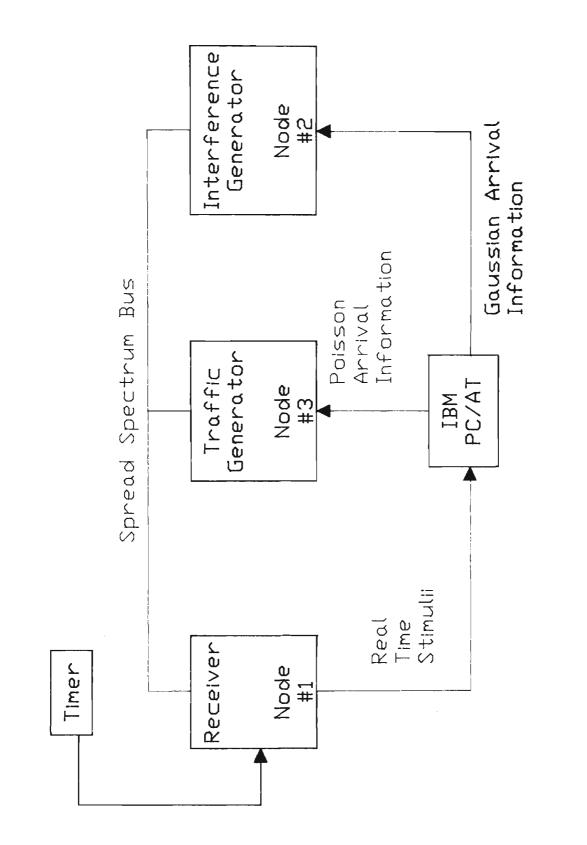

|     |         | 7.6.1    | Test Configuration and General Procedures                 | 124 |

|     |         | 7.6.2    | Test Results                                              | 127 |

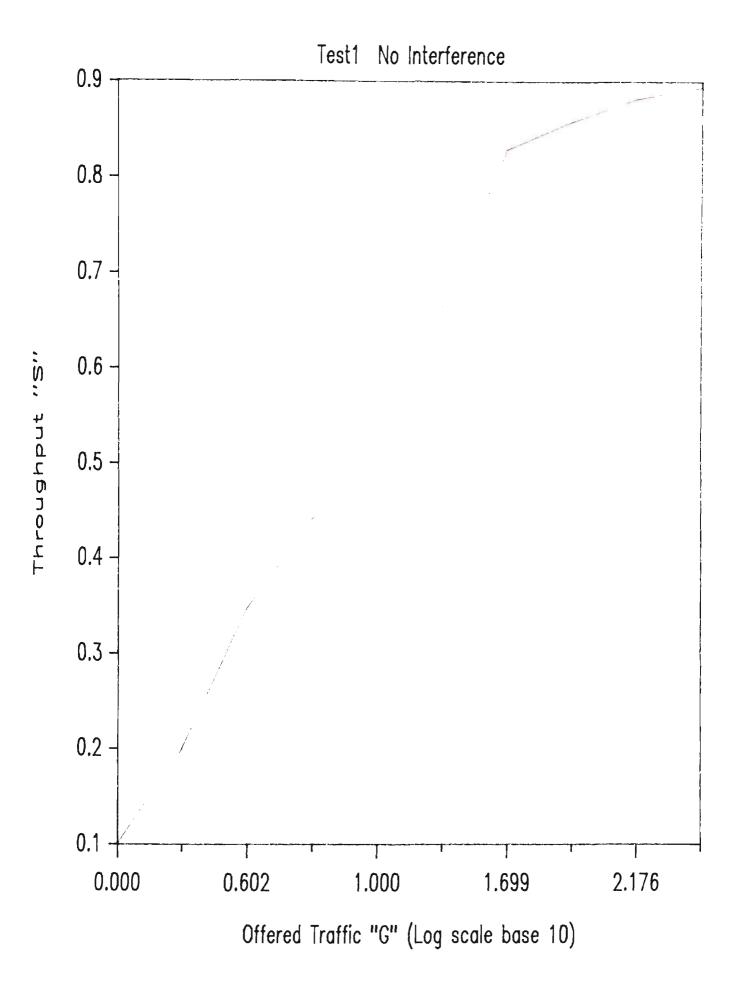

|     |         |          | 7.6.2.1 Test #1 Peak Channel Occupancy - no collisions    | 127 |

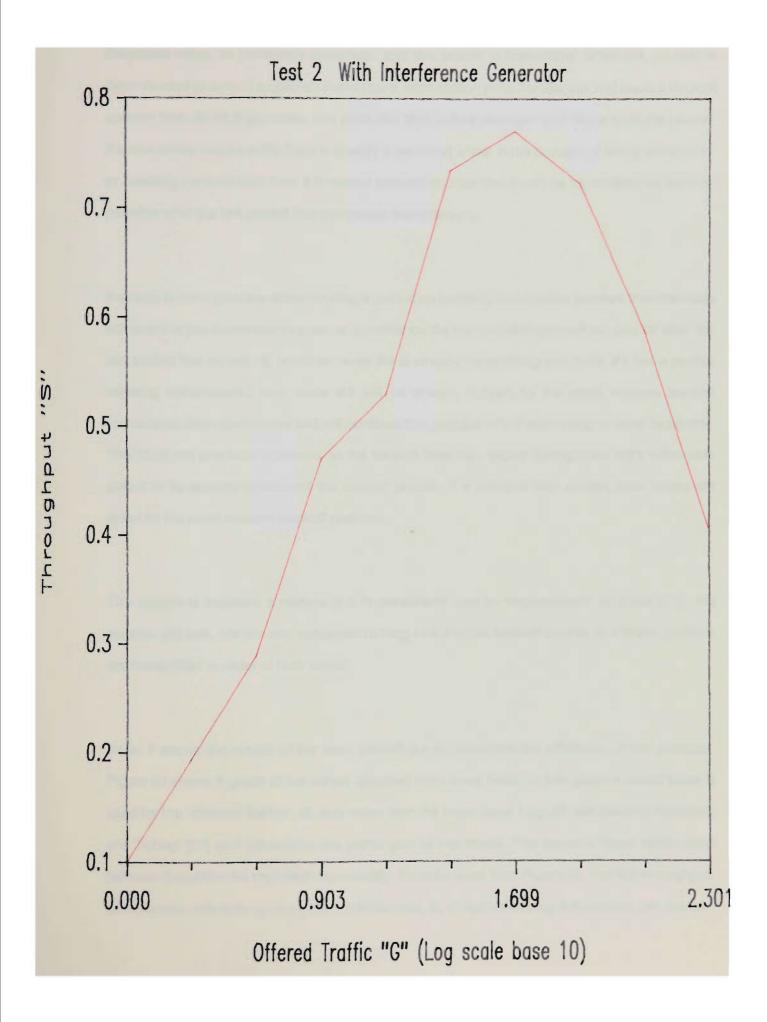

|     |         |          | 7.6.2.2 Test #2 Throughput - with collisions              | 130 |

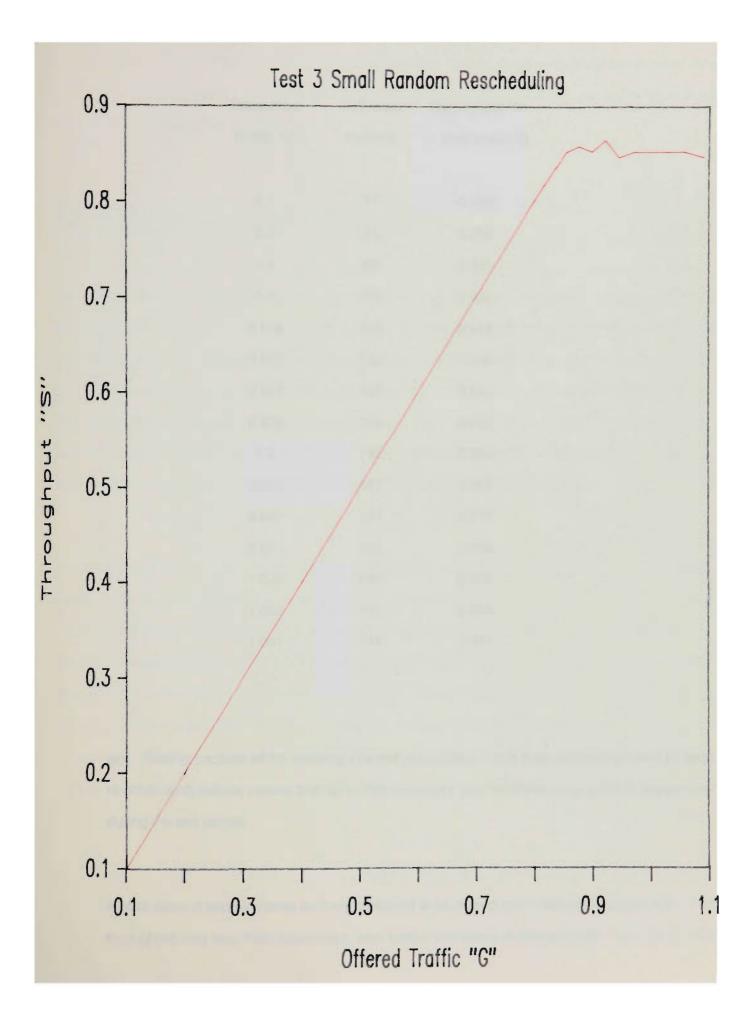

|     |         |          | 7.6.2.3 Test #3 Short (Pseudo random) Re-scheduling Times | 131 |

|     | 7.7     | Analys   | is of System Performance                                  | 136 |

|     |         |          |                                                           |     |

| 8   | CONC    | LUSION   | S                                                         | 137 |

|     | 8.1     | Discus   | sion of the Project                                       | 137 |

|     | 8.2     | Compa    | arison With Other Networks                                | 140 |

|     | 8.3     | Sugge    | stions for Future Work                                    | 142 |

|     |         |          |                                                           |     |

|     | Bibliog | raphy    |                                                           | 144 |

|     |         |          |                                                           |     |

| App | endic   | es       |                                                           |     |

|     |         |          |                                                           |     |

|     |         |          |                                                           |     |

| A   |         | IT DIAGI |                                                           | 150 |

|     | A.1     | Summa    | ary                                                       | 150 |

| _   |         |          |                                                           |     |

| В   |         | GENEF    |                                                           | 157 |

|     | B.1     | Summa    | ary                                                       | 157 |

iv

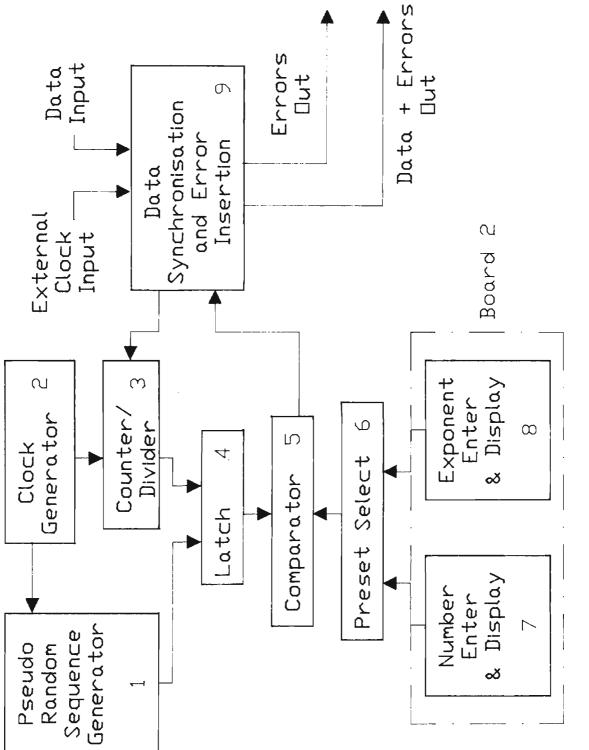

| B.2   | The Requirements                                                                                                                                                                                                                                   | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

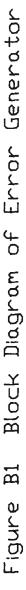

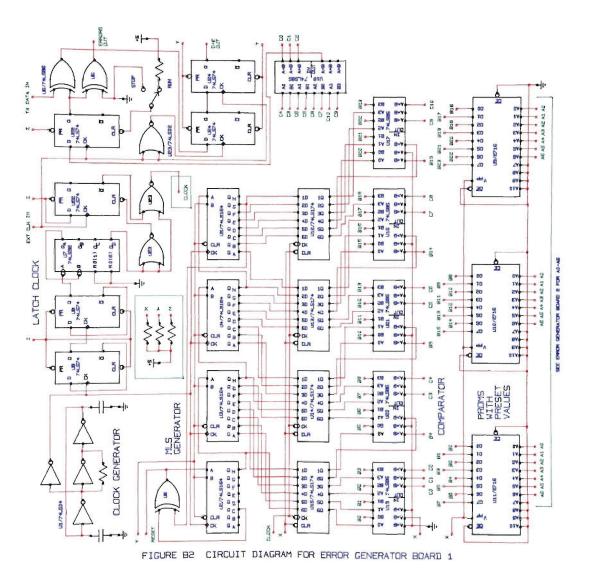

| B.3   | Circuit Description                                                                                                                                                                                                                                | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

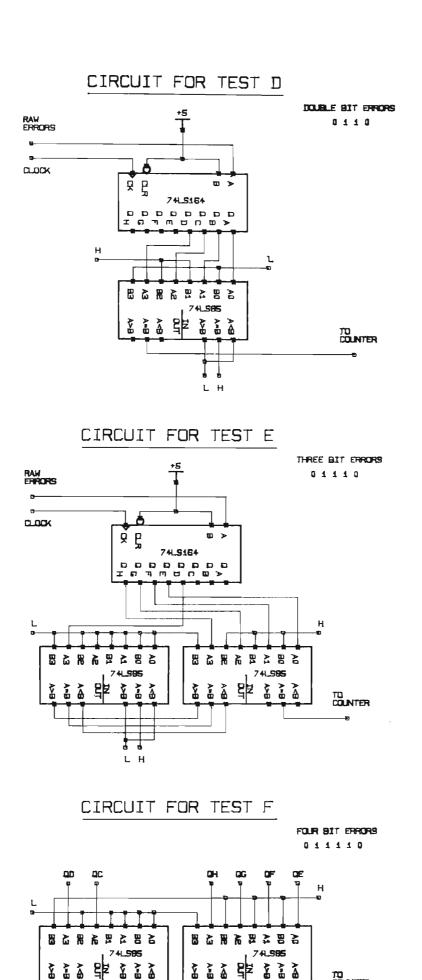

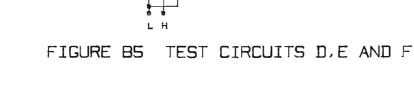

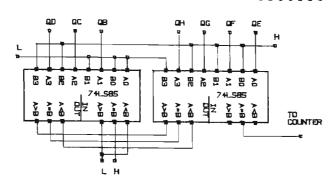

| B.4   | Circuit Testing and Discussion of Results                                                                                                                                                                                                          | 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

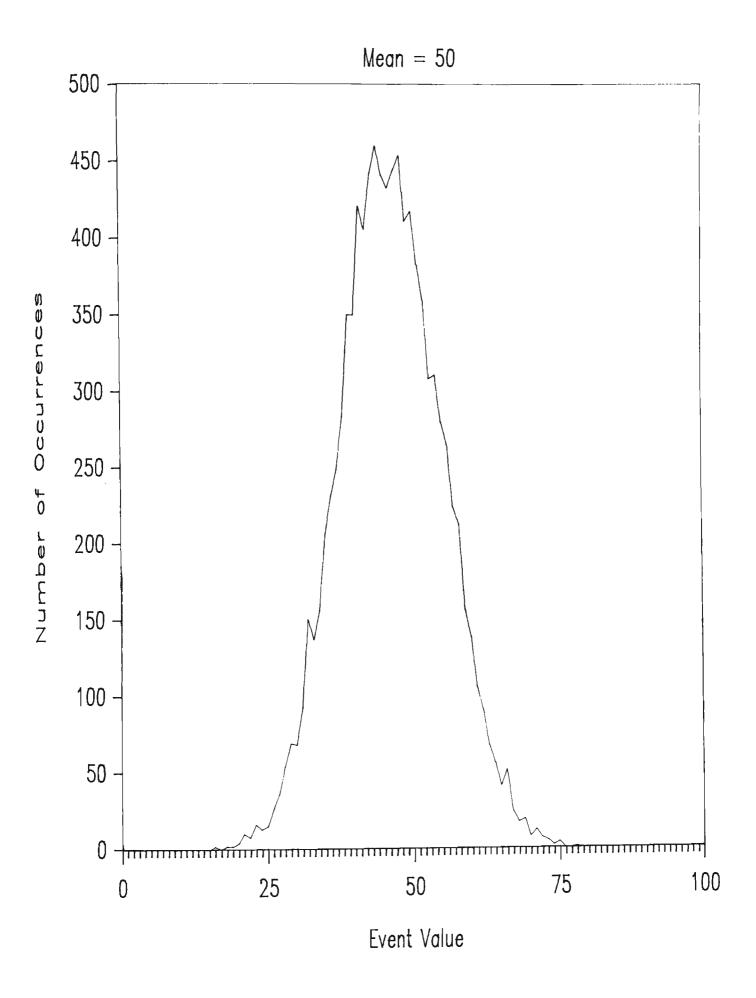

|       | B.4.1 Test #1                                                                                                                                                                                                                                      | 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

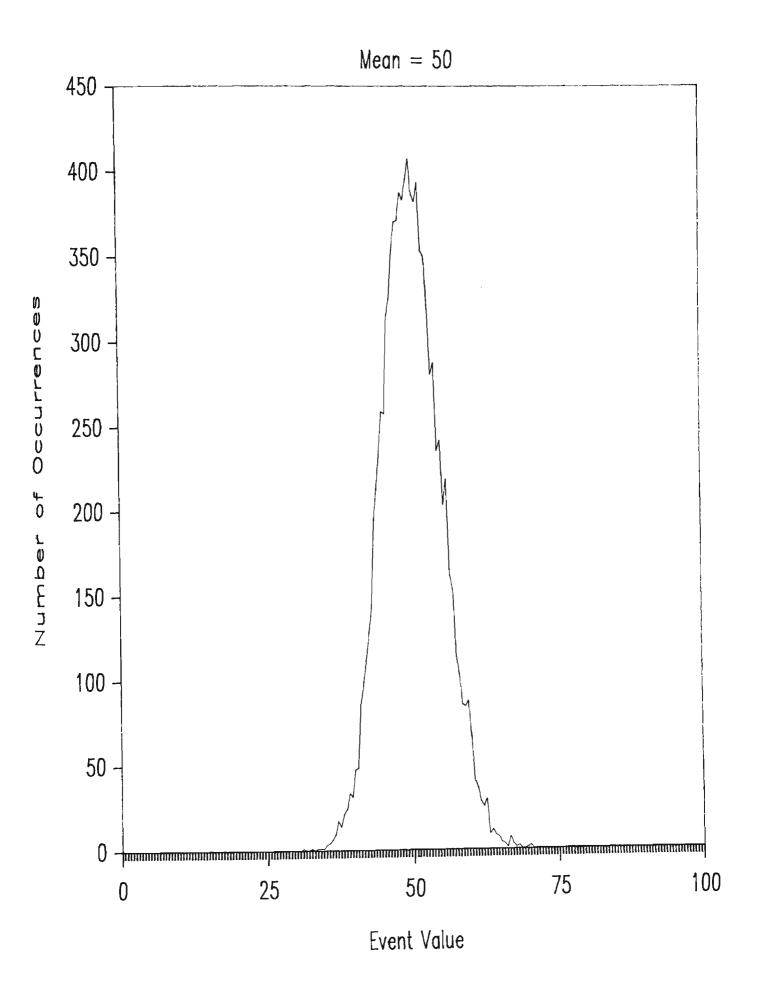

|       | B.4.2 Test #2                                                                                                                                                                                                                                      | 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | B.4.3 Test #3                                                                                                                                                                                                                                      | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | B.4.4 Tests #4 to #8                                                                                                                                                                                                                               | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | B.4.5 Tests #9 and #10                                                                                                                                                                                                                             | 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | B.4.6 Tests #11 and #12                                                                                                                                                                                                                            | 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| B.5   | Appendix B Conclusions                                                                                                                                                                                                                             | 189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | VALOGUE MULTIPLIER                                                                                                                                                                                                                                 | 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C.1   | Summary                                                                                                                                                                                                                                            | 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

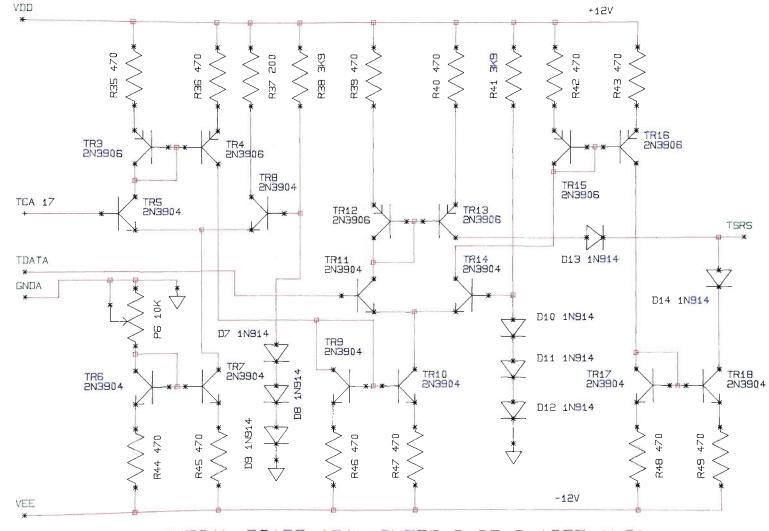

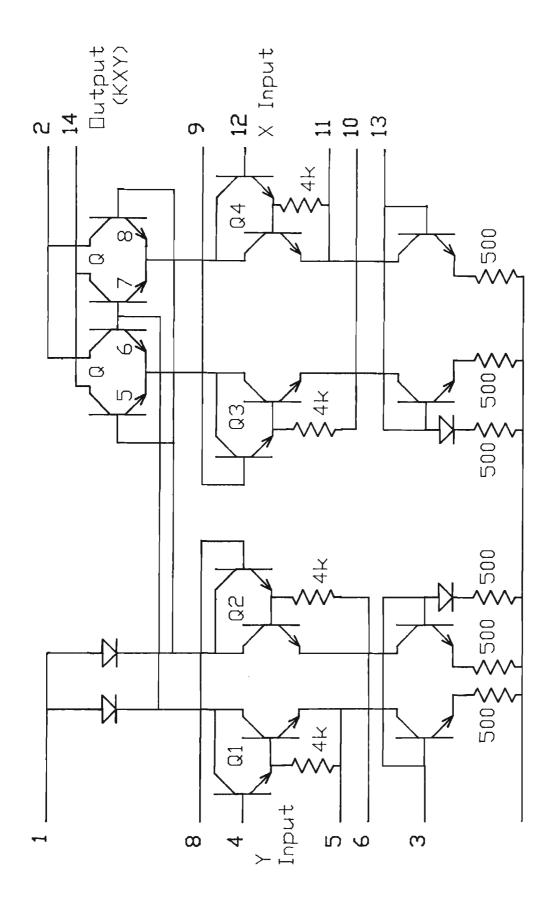

| C.2   | Theory of Operation                                                                                                                                                                                                                                | 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C.3   | Level Shifting                                                                                                                                                                                                                                     | 195                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

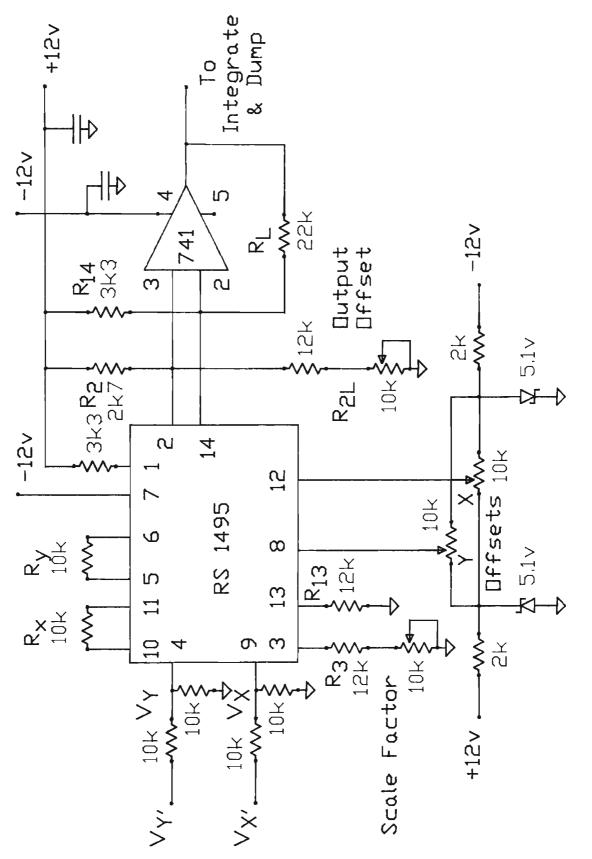

| C.4   | Analogue Multiplier Design Procedure                                                                                                                                                                                                               | 196                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C.5   | Level Shifter Design                                                                                                                                                                                                                               | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PROGF | AM - CSMA/CD SIMULATOR                                                                                                                                                                                                                             | 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D.1   | Summary                                                                                                                                                                                                                                            | 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D.2   | Brief Outline of the Program                                                                                                                                                                                                                       | 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PROGF | RAM LISTING                                                                                                                                                                                                                                        | 204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MICRO | PROCESSOR PROGRAM                                                                                                                                                                                                                                  | 209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| E.1   | Summary                                                                                                                                                                                                                                            | 209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PROGF | AM LISTING                                                                                                                                                                                                                                         | 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PROGF | AM - TRAFFIC GENERATOR                                                                                                                                                                                                                             | 231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F.1   | Summary                                                                                                                                                                                                                                            | 231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F.2   | Poisson & Normal Distribution Characteristics                                                                                                                                                                                                      | 231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | <ul> <li>B.3</li> <li>B.4</li> <li>B.5</li> <li>THE AN</li> <li>C.1</li> <li>C.2</li> <li>C.3</li> <li>C.4</li> <li>C.5</li> <li>PROGE</li> <li>D.1</li> <li>D.2</li> <li>PROGE</li> <li>MICRO</li> <li>E.1</li> <li>PROGE</li> <li>F.1</li> </ul> | <ul> <li>B.3 Circuit Testing and Discussion of Results</li> <li>B.4.1 Test #1</li> <li>B.4.2 Test #2</li> <li>B.4.3 Test #3</li> <li>B.4.4 Tests #4 to #8</li> <li>B.4.5 Tests #9 and #10</li> <li>B.4.6 Tests #11 and #12</li> <li>B.5 Appendix B Conclusions</li> </ul> THE ANALOGUE MULTIPLIER C.1 Summary C.2 Theory of Operation C.3 Level Shifting C.4 Analogue Multiplier Design Procedure C.5 Level Shifter Design PROGRAM - CSMA/CD SIMULATOR D.1 Summary D.2 Brief Outline of the Program PROGRAM LISTING PROGRAM - TRAFFIC GENERATOR F.1 Summary PROGRAM - TRAFFIC GENERATOR F.1 Summary |

|                 | F.2.1  | Normal (Gaussian)           | 231 |

|-----------------|--------|-----------------------------|-----|

|                 | F.2.2  | Poisson                     | 232 |

| F.3             | The "R | andom" Programs             | 233 |

|                 | F.3.1  | Normal Distribution Numbers | 233 |

|                 | F.3.2  | Poisson Number Program      | 234 |

| F.4             | The Tr | affic Program               | 234 |

| PROGRAM LISTING |        |                             | 238 |

|                 |        |                             |     |

#### G PUBLICATIONS

| G.1 | Summary | 242 |

|-----|---------|-----|

|     |         |     |

242

## **List of Figures**

| Figure | Title                                               | Page |

|--------|-----------------------------------------------------|------|

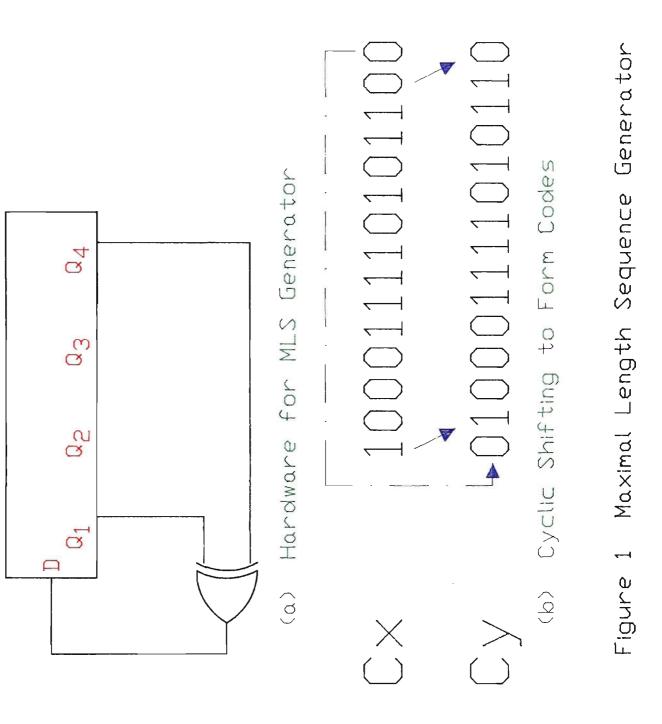

| 1      | Maximal Length Sequence Generator                   | 12   |

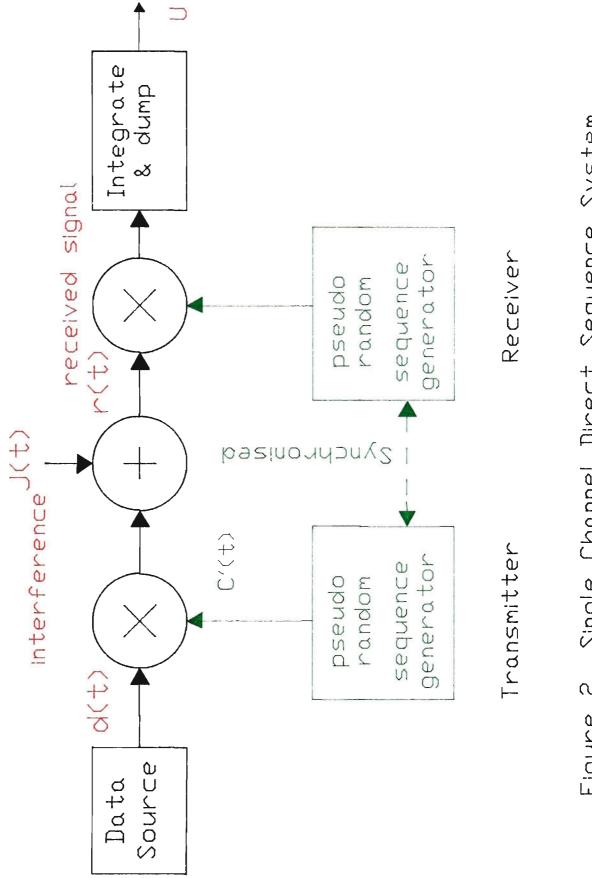

| 2      | Single Channel Direct Sequence System               | 14   |

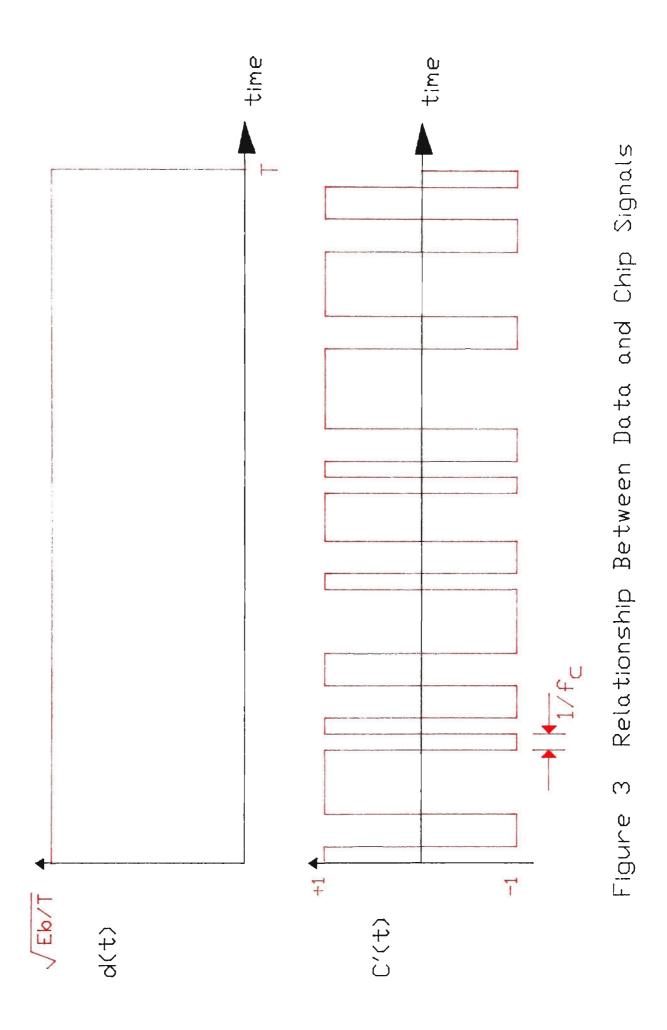

| 3      | Relationship Between Chip and Data Signals          | 15   |

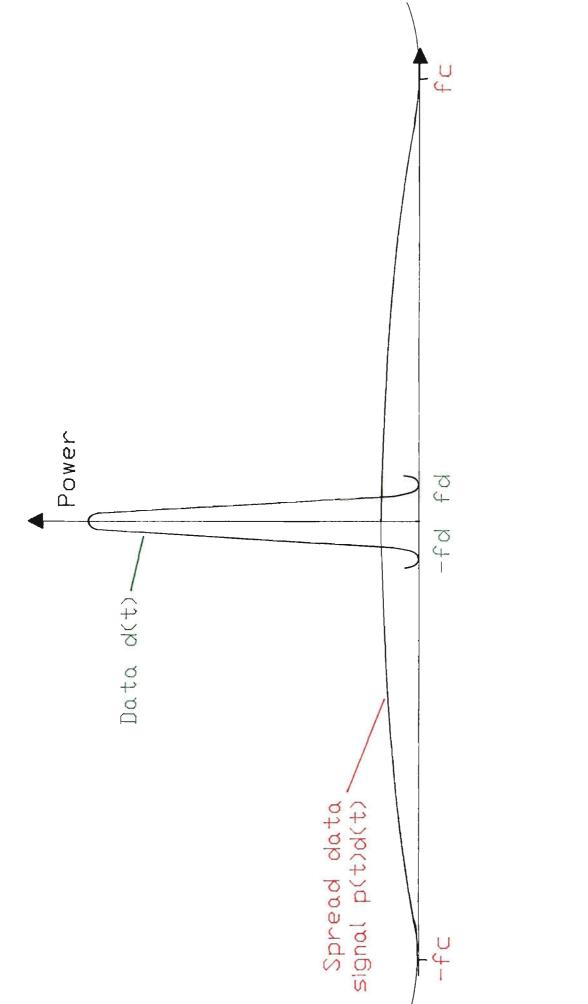

| 4      | Spectral Occupancy of Signals                       | 18   |

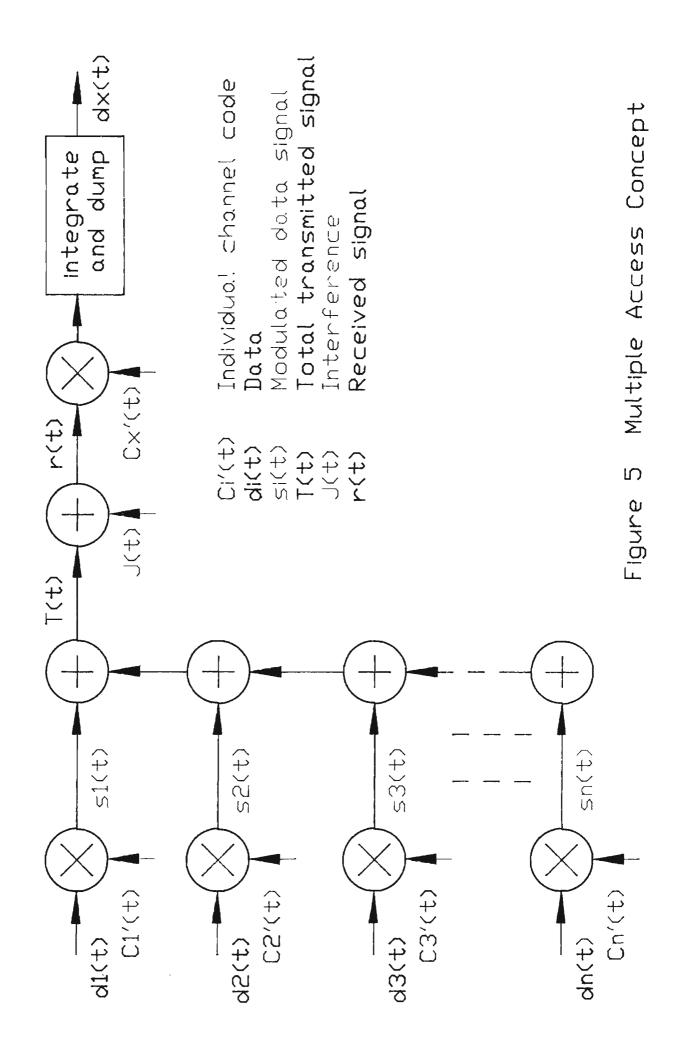

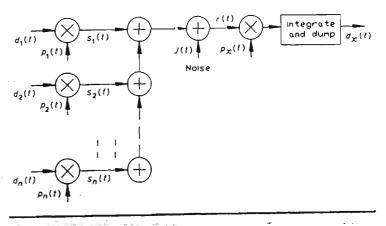

| 5      | Multiple Access Concept                             | 20   |

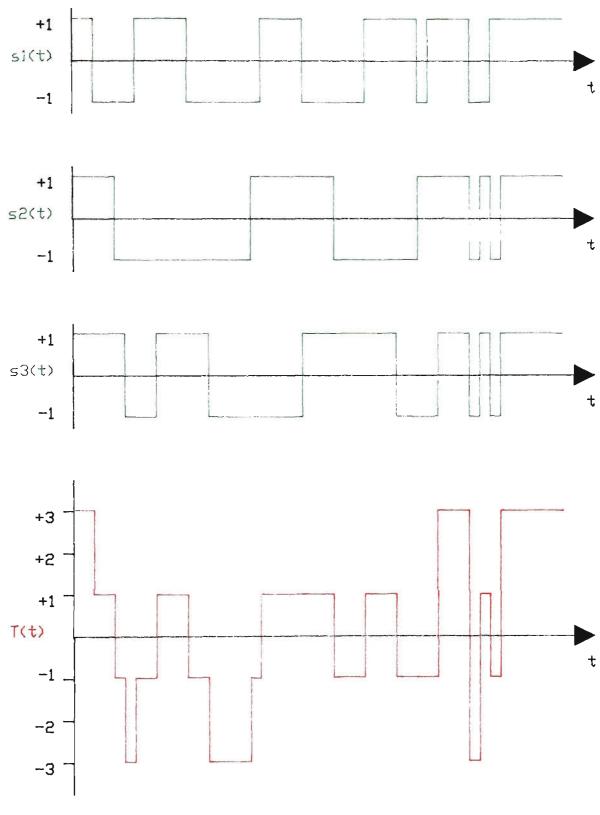

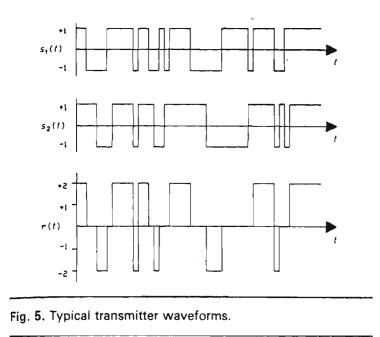

| 6      | Typical Transmitter Waveforms                       | 21   |

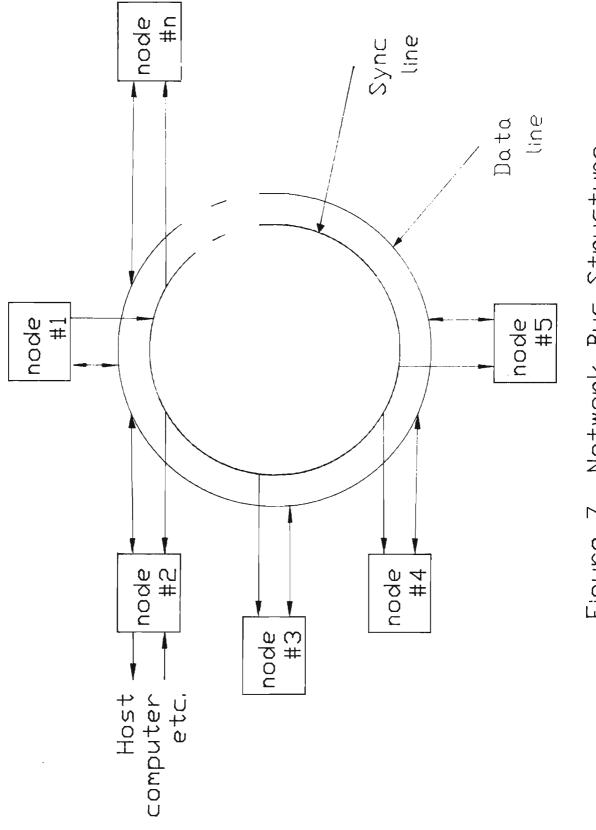

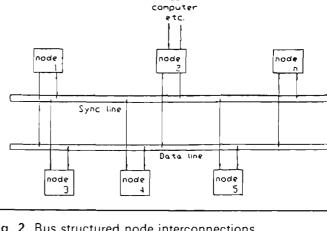

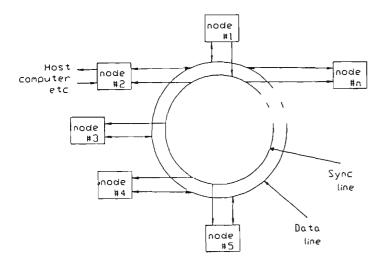

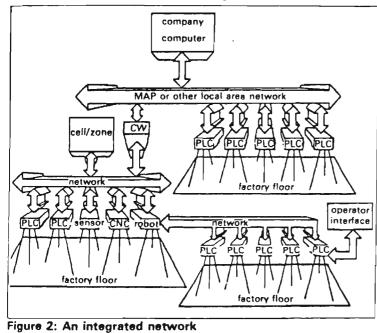

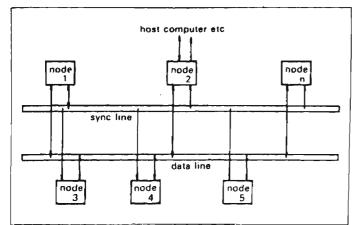

| 7      | Network Bus Structure                               | 26   |

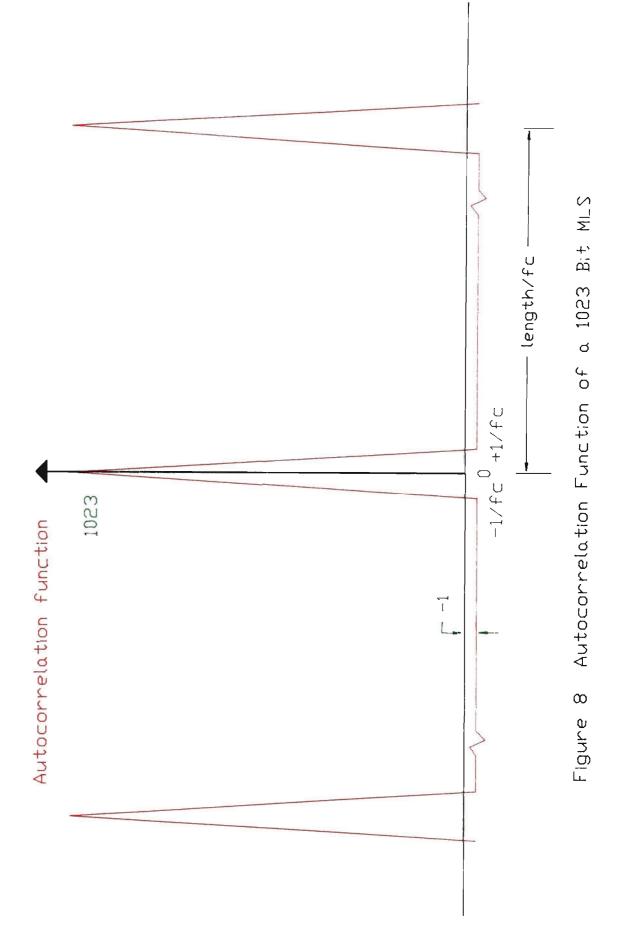

| 8      | Autocorrelation Function of a 1023 Bit MLS          | 33   |

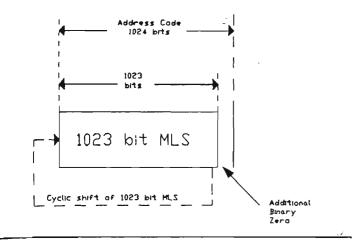

| 9      | "Modified" MLS Address Code Generation              | 35   |

| 10     | Autocorrelation Function of "Modified" 1024 Bit MLS | 36   |

| 11     | System Delay and Timing Aspects                     | 38   |

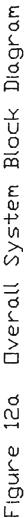

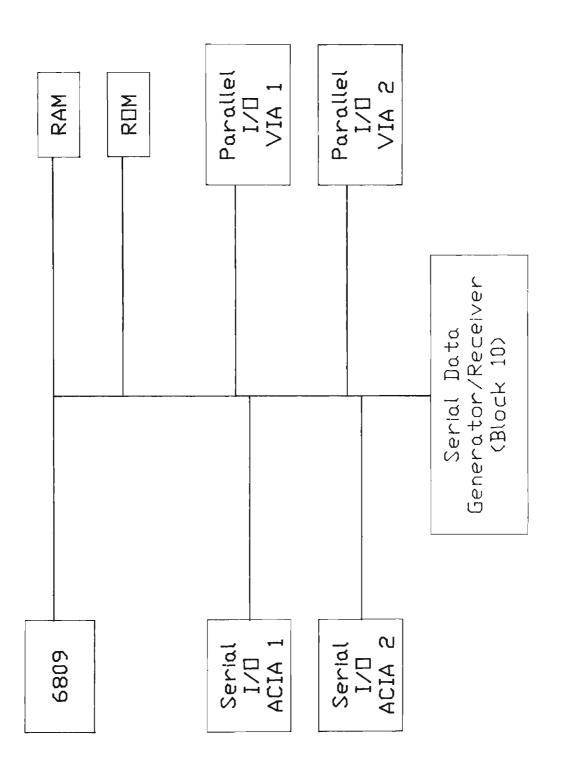

| 12a    | Overall System Block Diagram                        | 45   |

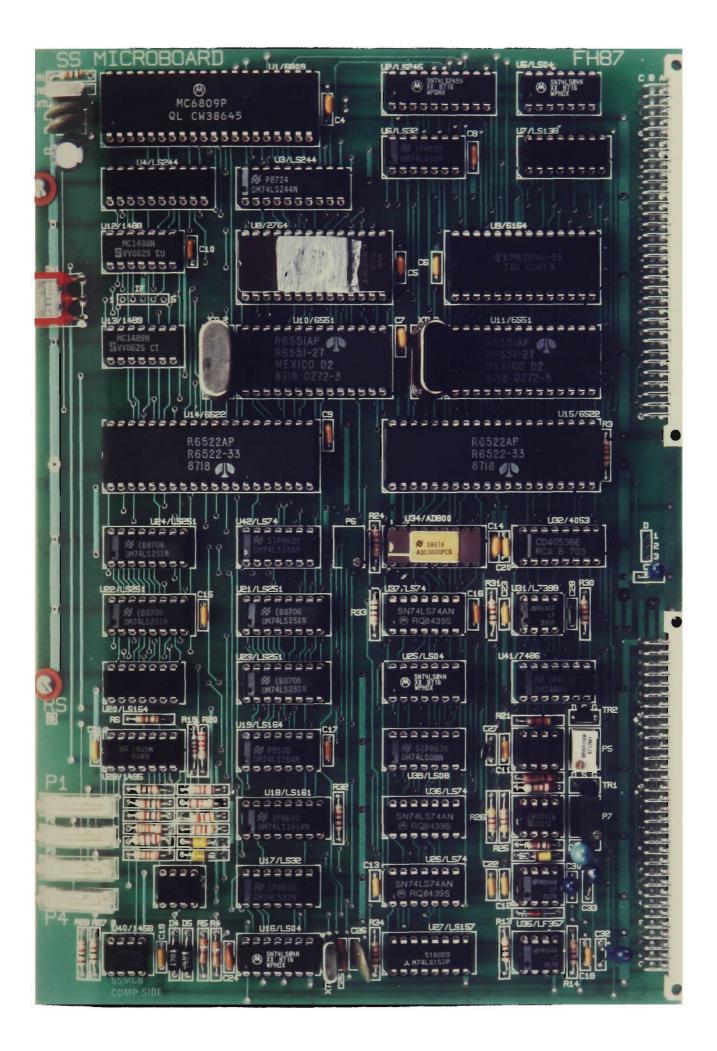

| 12b    | Photograph of Microprocessor Board                  | 46   |

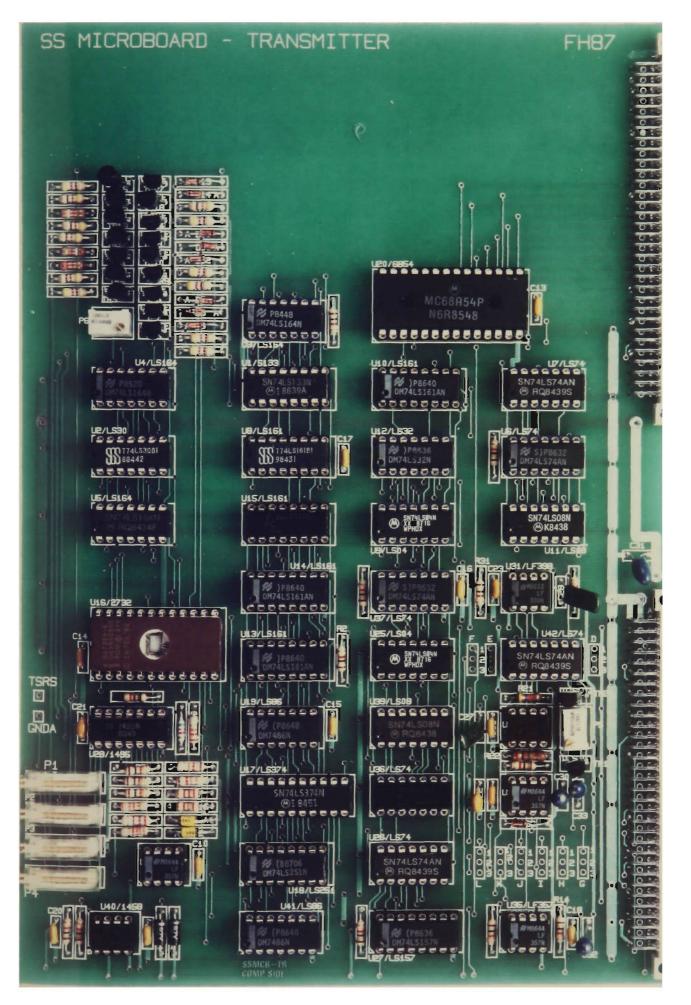

| 12c    | Photograph of Peripheral Board                      | 47   |

| 13     | Microprocessor Control Circuit - Block Diagram      | 51   |

| 14     | Memory Map for Microprocessor Control Circuit       | 53   |

| 15     | V.I.A. Control Signal Pin Connections               | 54   |

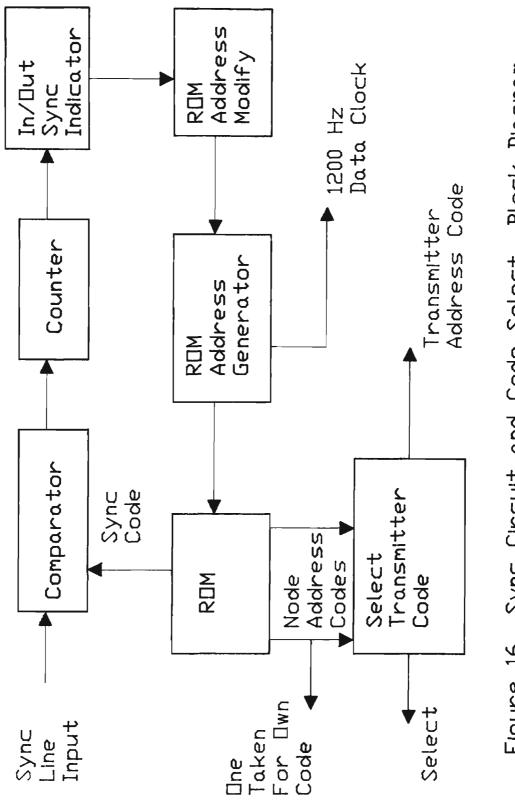

| 16     | Sync Circuit and Code Select - Block Diagram        | 55   |

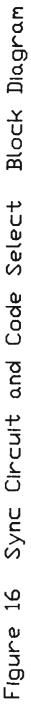

| 17     | Timing Diagram For Sync Circuit                     | 57   |

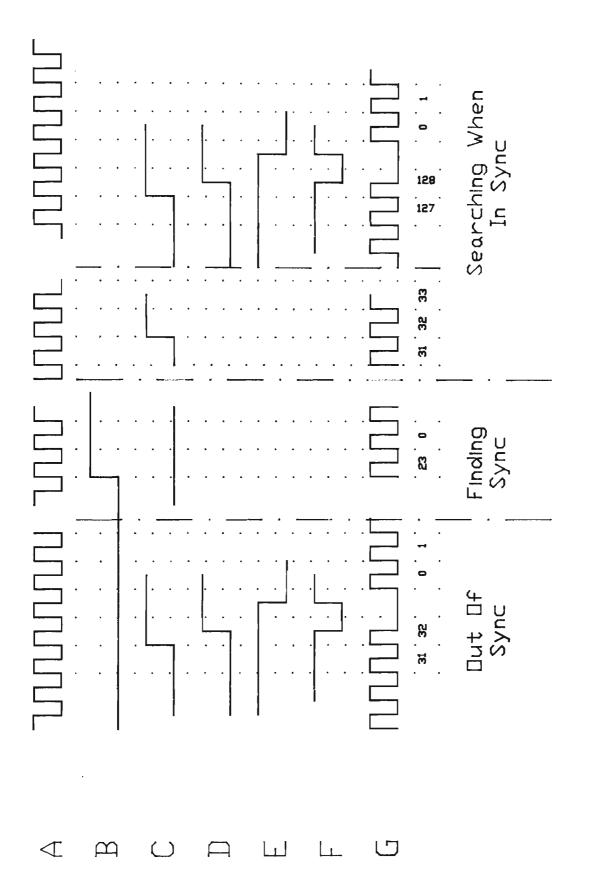

| 18     | Schematic Diagram for Synchronisation Circuit       | 58   |

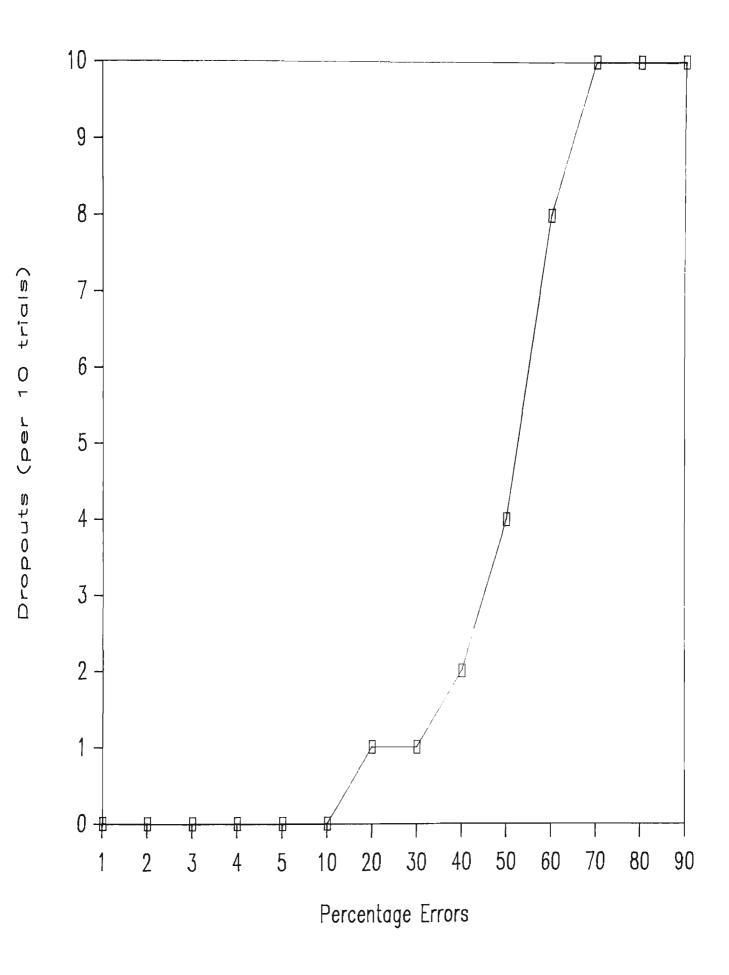

| 19     | Sync Dropout vs Error Rate                          | 62   |

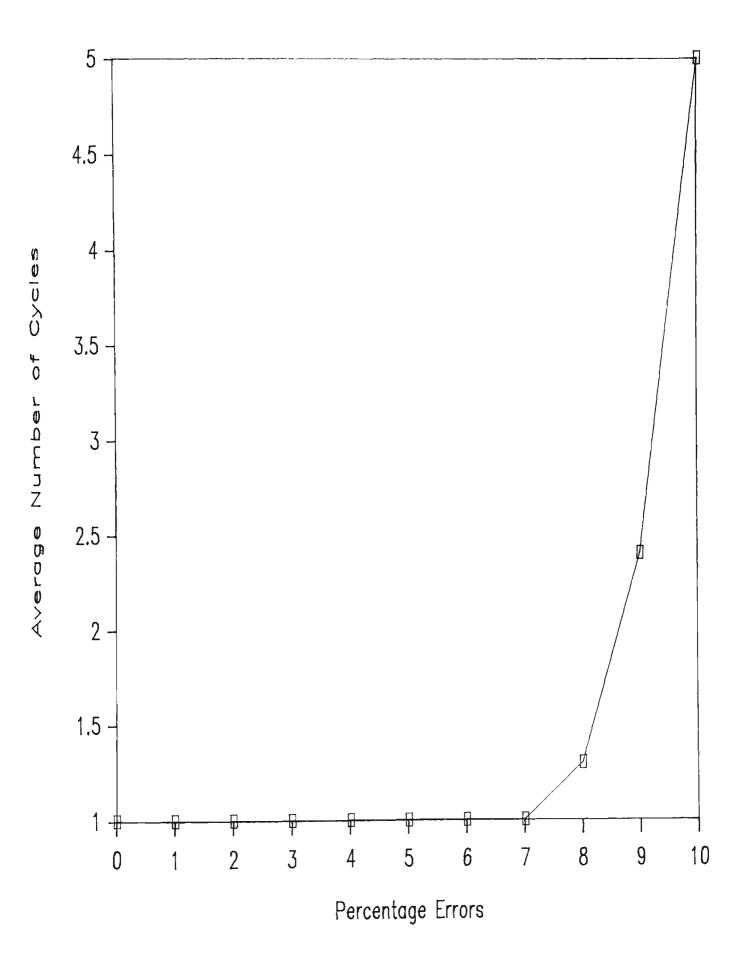

| 20     | Cycles to Regain Sync vs Error Rate                 | 64   |

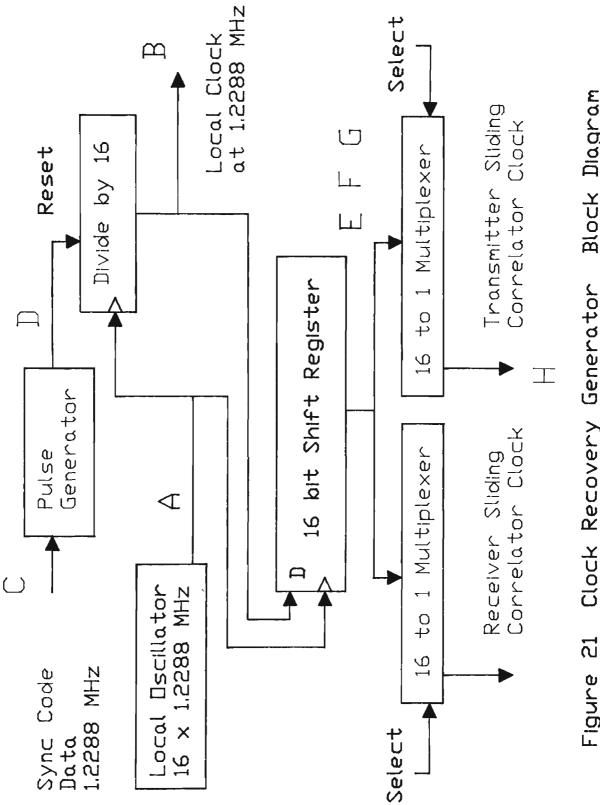

| 21     | Clock Recovery/Generator - Block Diagram            | 65   |

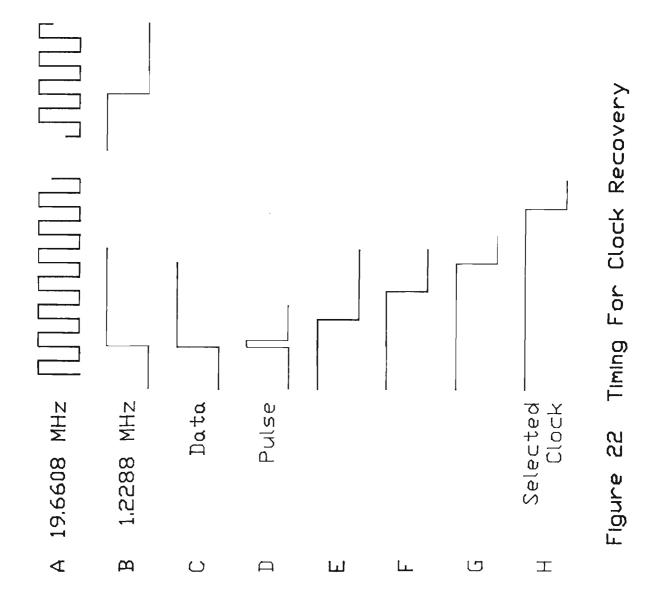

| 22     | Timing for Clock Recovery                           | 66   |

| 23     | Transmitter Line Driver - Block Diagram             | 69   |

| 24     | Line Driver - Circuit Schematic                     | 71   |

|        |                                                     |      |

#### Figure

| 25          | A to D Converter Circuit - Block Diagram                      | 73  |

|-------------|---------------------------------------------------------------|-----|

| 26          | Receiver Circuít - Block Diagram                              | 75  |

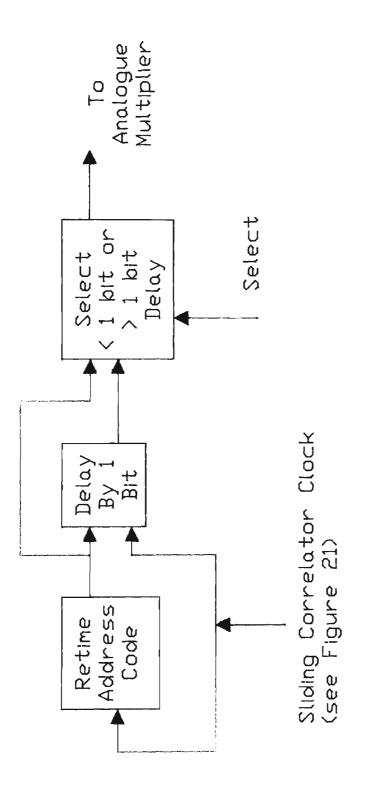

| 27          | Sliding Correlator - Block Diagram                            | 77  |

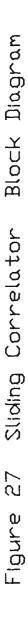

| 28          | Analogue Multiplier - Block Diagram                           | 78  |

| 29          | Integrate and Dump Circuit and Timing Diagram                 | 80  |

| 30          | Transmitter Circuit - Block Diagram                           | 82  |

| 31          | Bit Error Rate Test Hardware Configuration                    | 84  |

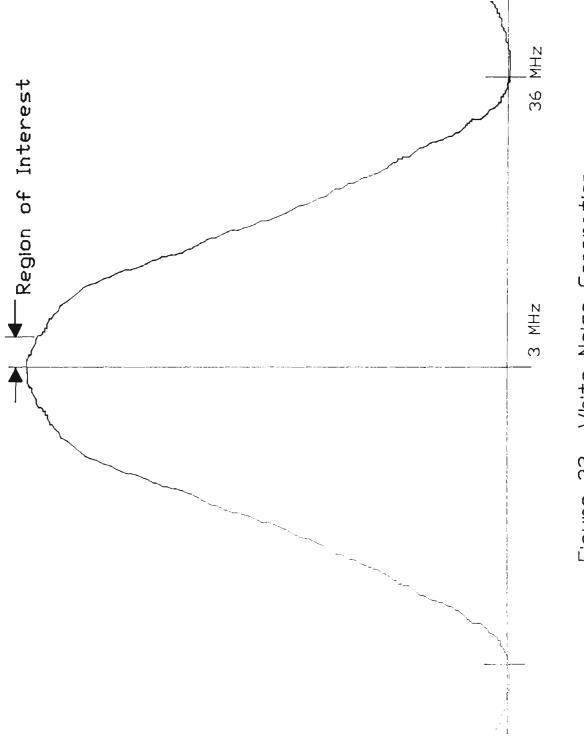

| 32          | White Noise Generation                                        | 85  |

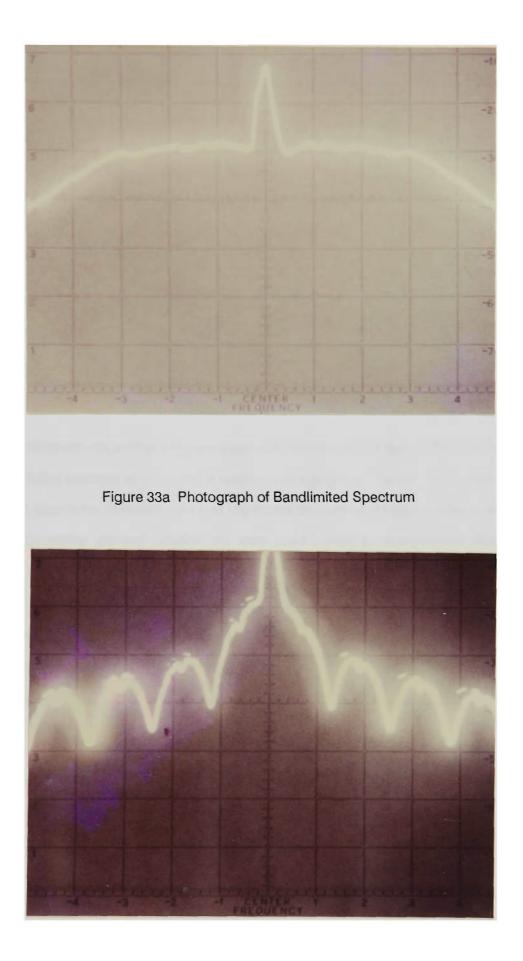

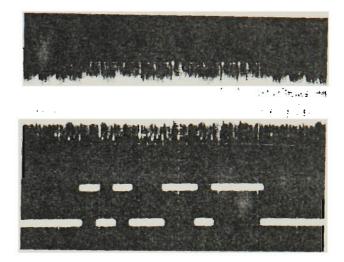

| 33a         | Photograph of Band Limited Spectrum                           | 86  |

| <b>33</b> b | Photograph of Single Transmitter Spectrum                     | 86  |

| 33c         | Photograph of Noise + Multi-Transmitters Spectrum             | 88  |

| 33d         | Photograph of Received Signal / Recovered Data                | 88  |

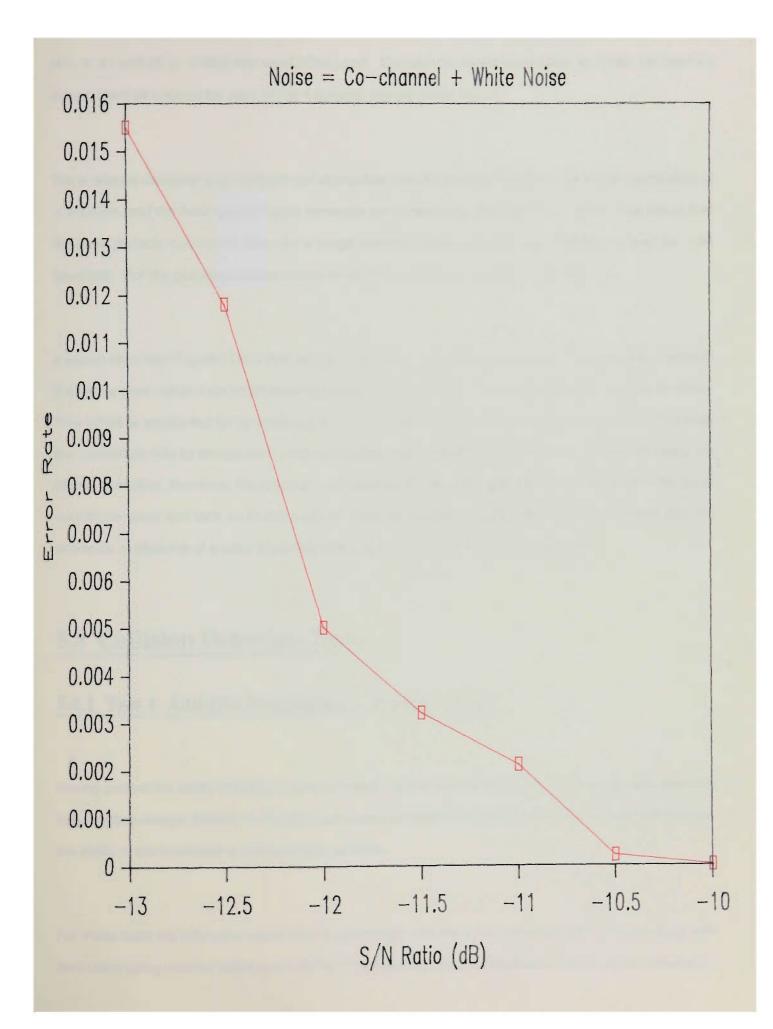

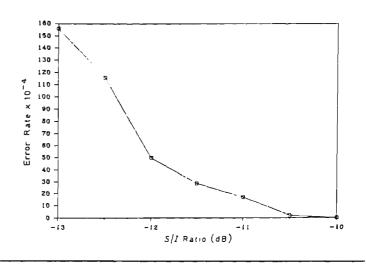

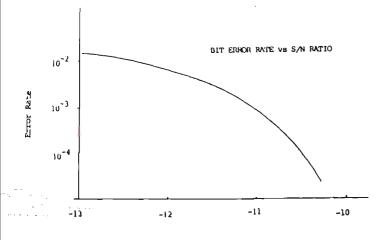

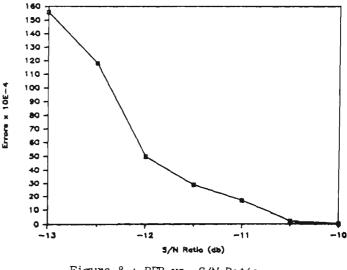

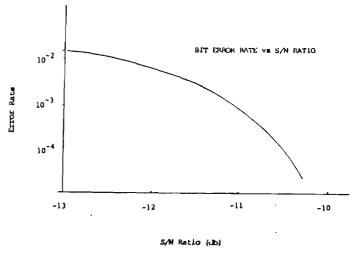

| 34          | Bit Error Rate vs S/N Ratio                                   | 90  |

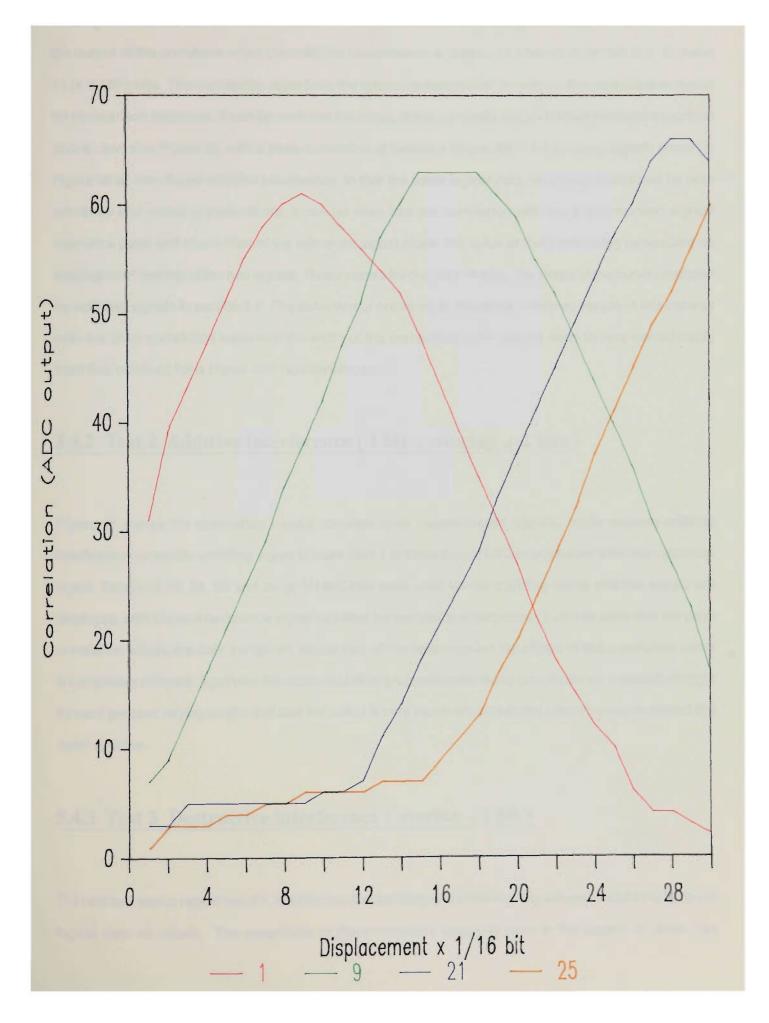

| 35          | Correlation With Delayed Signals                              | 92  |

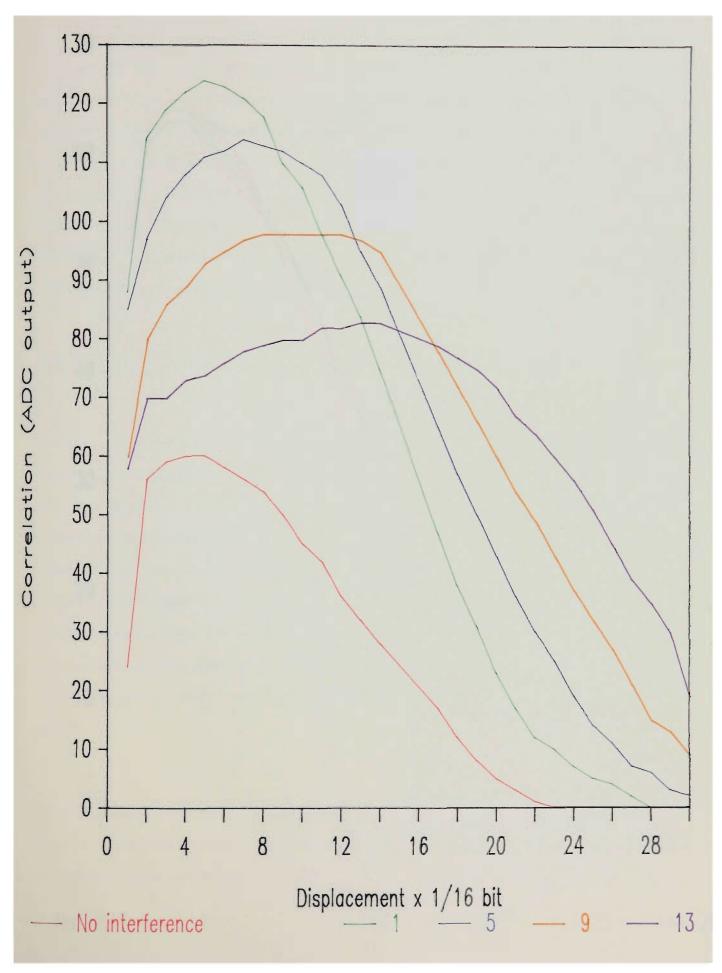

| 36          | Correlation of Additive Signals - Less Than 1 Bit Delay       | 94  |

| 37          | Correlation of Additive Signals - Greater Than 1 Bit Delay    | 95  |

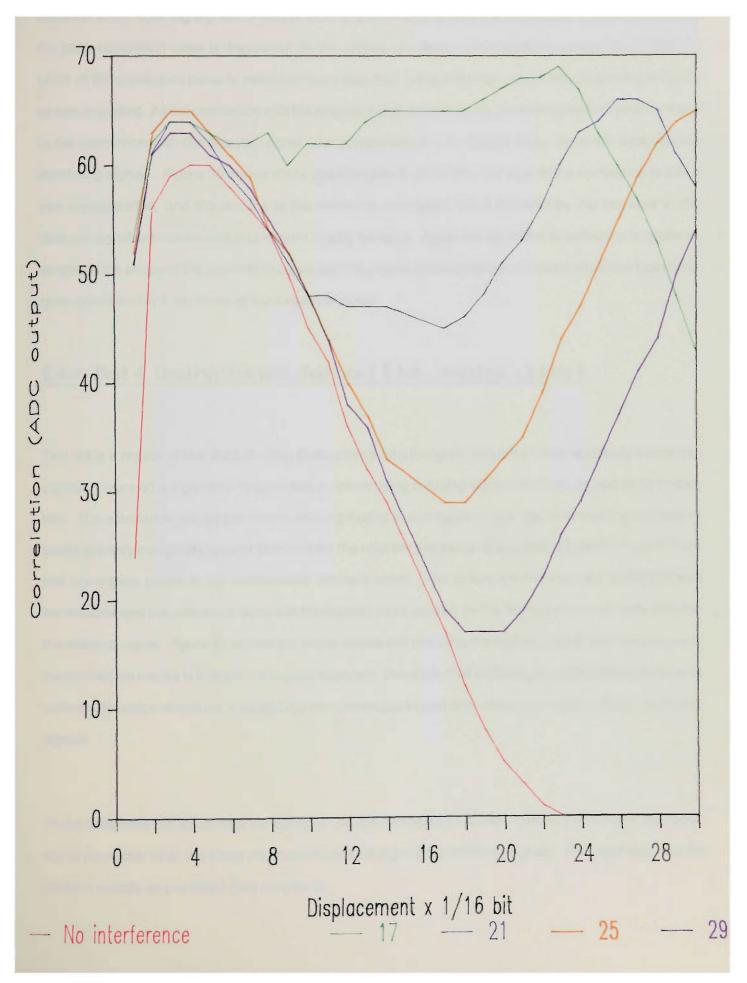

| 38          | Correlation of Destructive Signals - Less Than 1 Bit Delay    | 97  |

| 39          | Positive and Negative Correlation - Less Than 1 Bit Delay     | 98  |

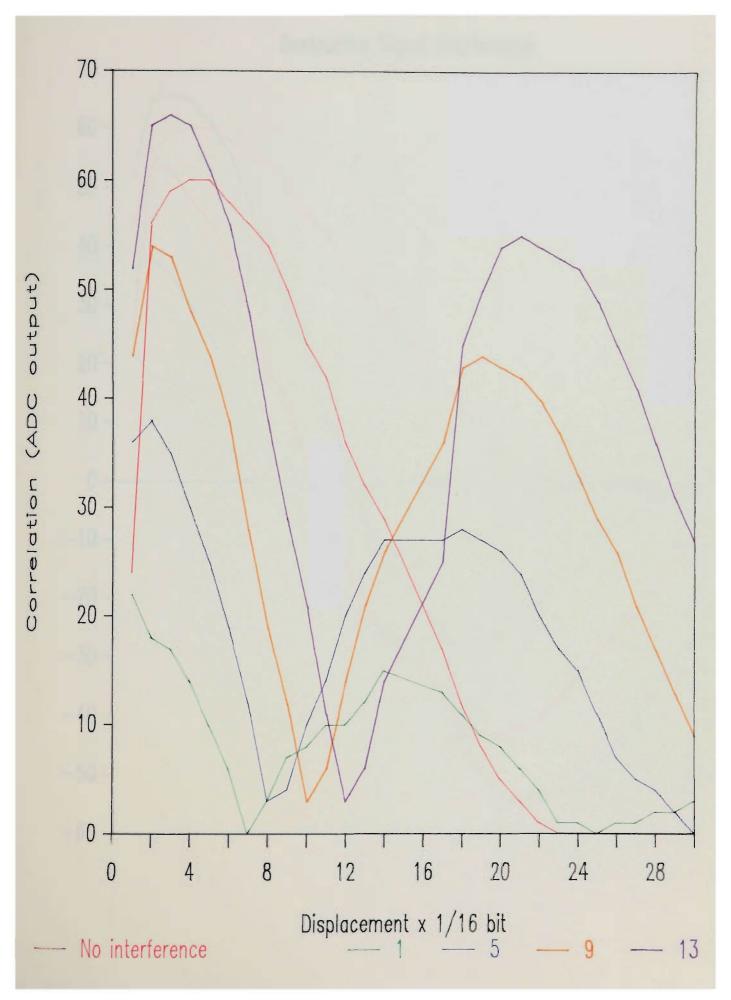

| 40          | Correlation of Destructive Signals - Greater Than 1 Bit Delay | 99  |

| 41          | Positive and Negative Correlation - Greater Than 1 Bit Delay  | 100 |

| 42          | Channel Transmission Characteristics                          | 104 |

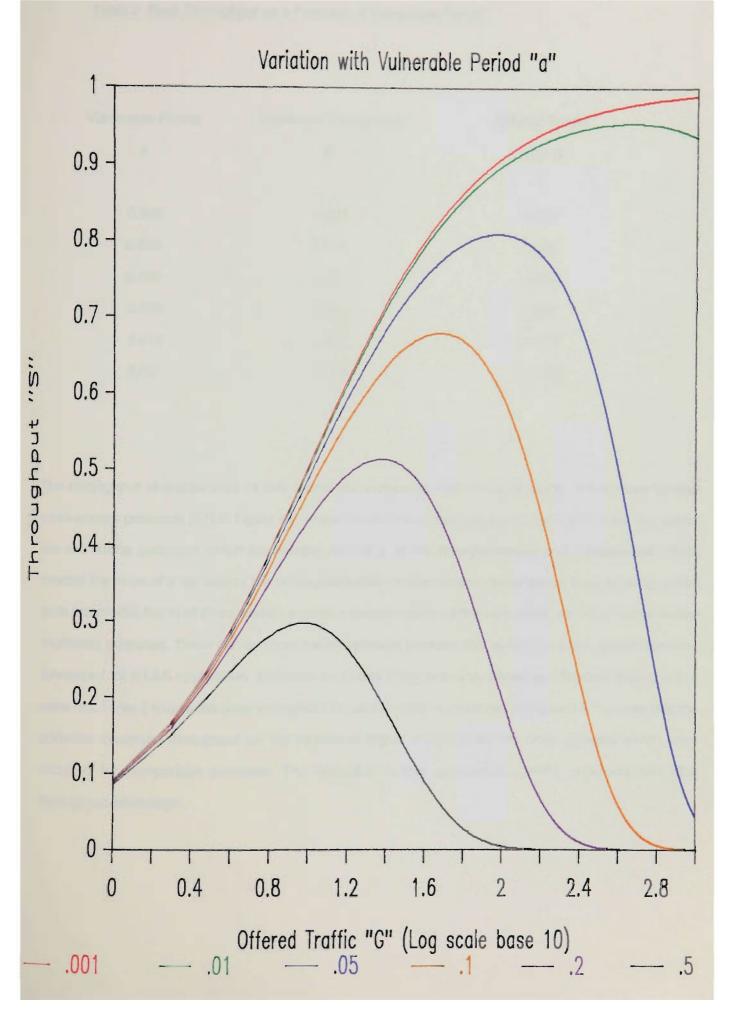

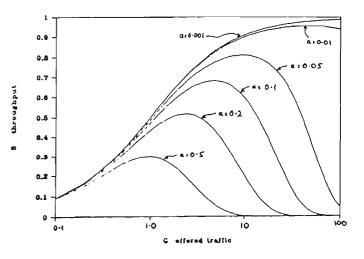

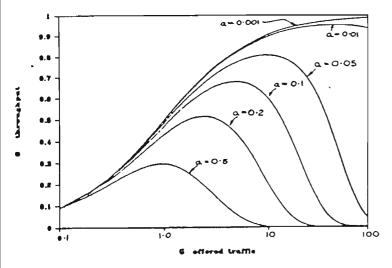

| 43          | Throughput vs Offered Traffic                                 | 107 |

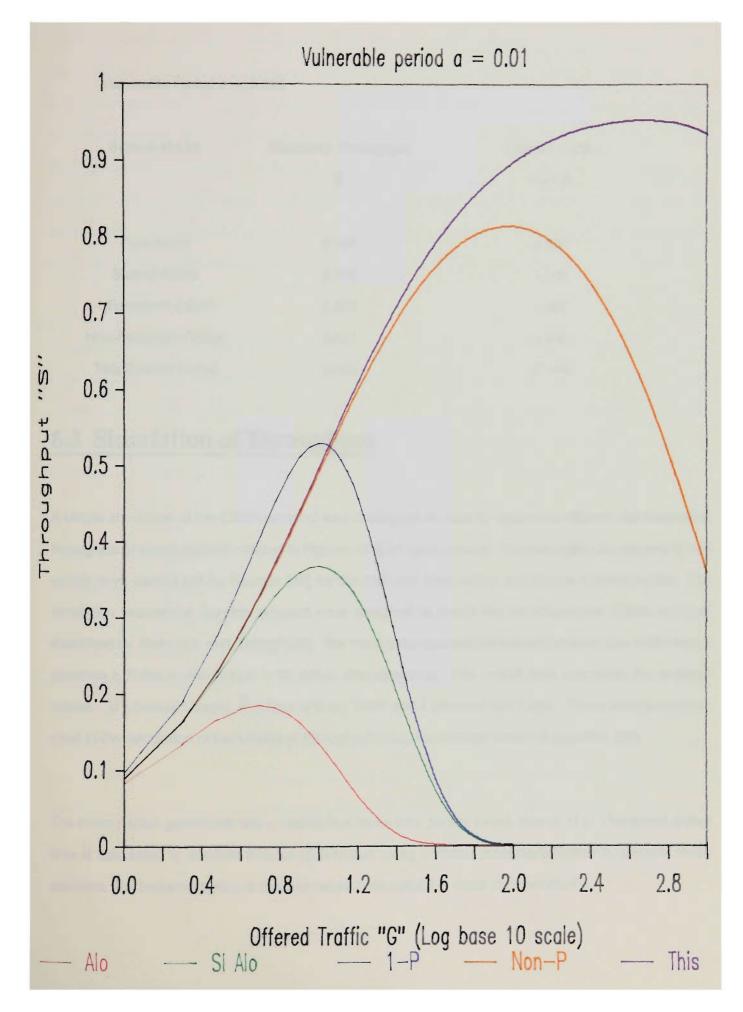

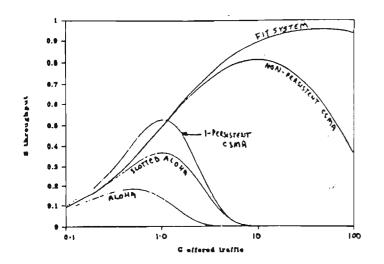

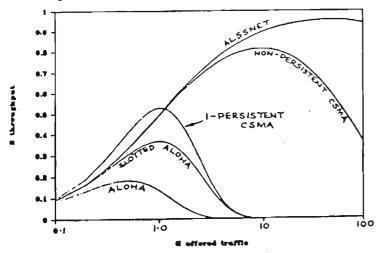

| 44          | Comparison of Throughput Characteristics                      | 109 |

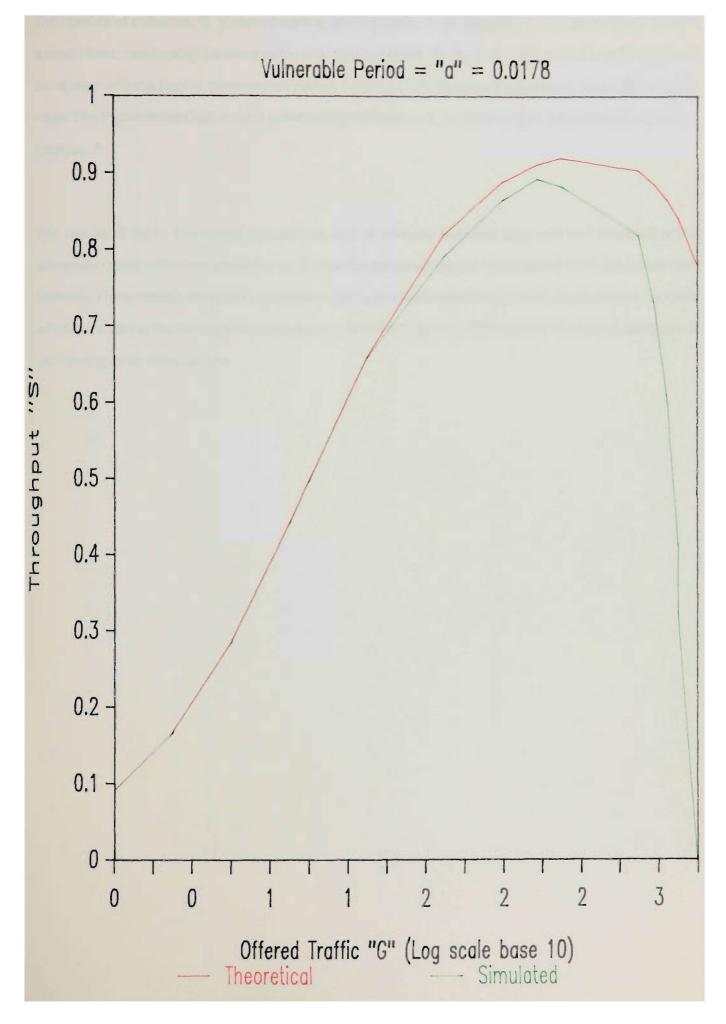

| 45          | Theoretical and Simulated Throughput                          | 113 |

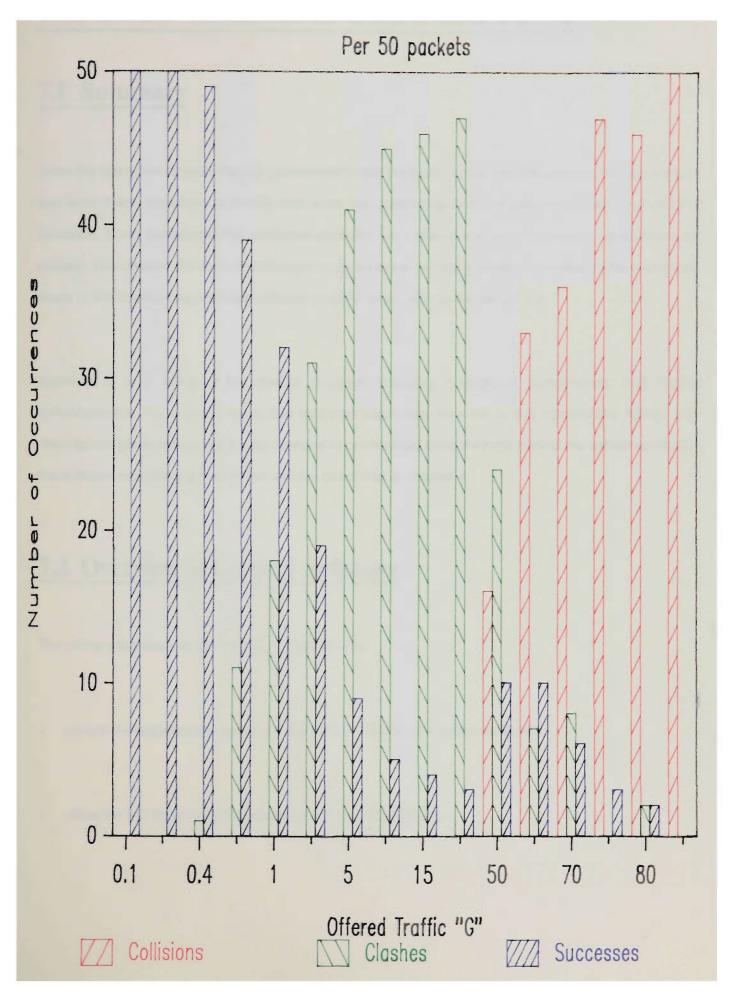

| 46          | Number of Collisions vs Offered Traffic                       | 115 |

| 47          | Hardware Configuration for Performance Tests                  | 125 |

| 48          | System Throughput - No Interference                           | 129 |

| 49          | System Throughput - With Interference Generator               | 132 |

Title

Page

| Figure | Title                                                                | Page |

|--------|----------------------------------------------------------------------|------|

| 50     | System Throughput - Alternative Protocol (small random rescheduling) | 134  |

| A1     | Microprocessor Board (M) - sheet 1 of 2                              | 151  |

| A2     | Microprocessor Board (M) - sheet 2 of 2                              | 152  |

| A3     | Peripheral Board (P) - sheet 1 of 3                                  | 153  |

| A4     | Peripheral Board (P) - sheet 2 of 3                                  | 154  |

| A5     | Peripheral Board (P) - sheet 3 of 3                                  | 155  |

| B1     | Block Diagram for Error Generator                                    | 159  |

| B2     | Circuit Diagram for Error Generator - Board 1                        | 162  |

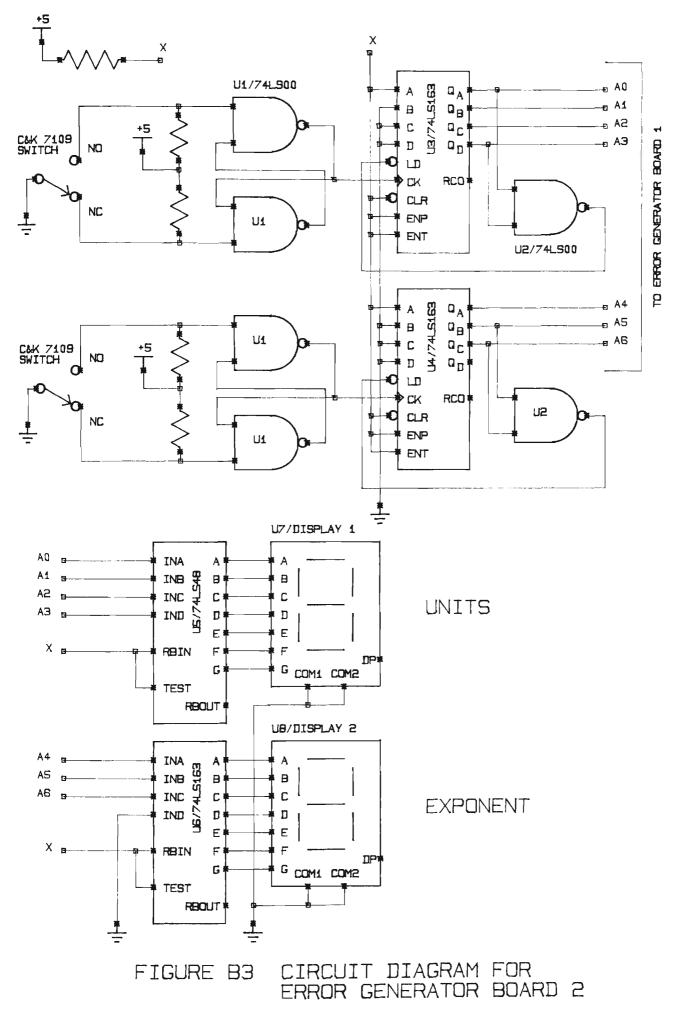

| B3     | Circuit Diagram for Error Generator - Board 2                        | 163  |

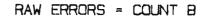

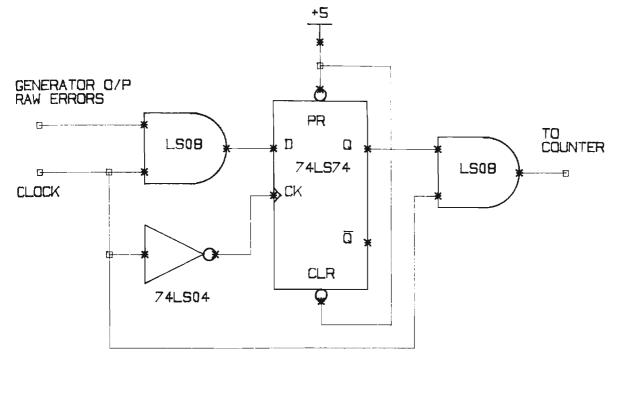

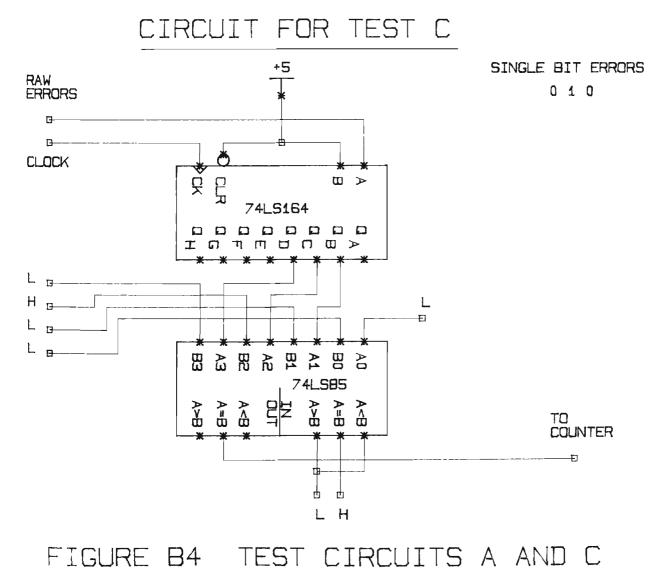

| B4     | Test Circuits A and C                                                | 168  |

| B5     | Test Circuits D, E and F                                             | 169  |

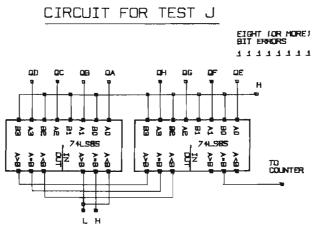

| B6     | Test Circuits G,H,I and J                                            | 170  |

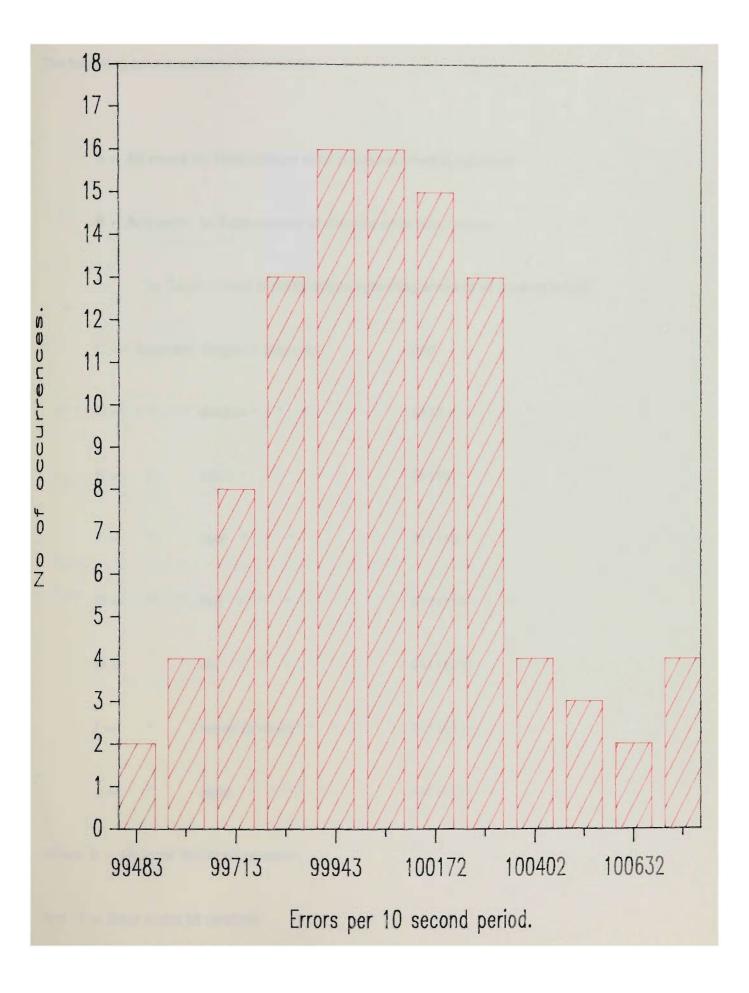

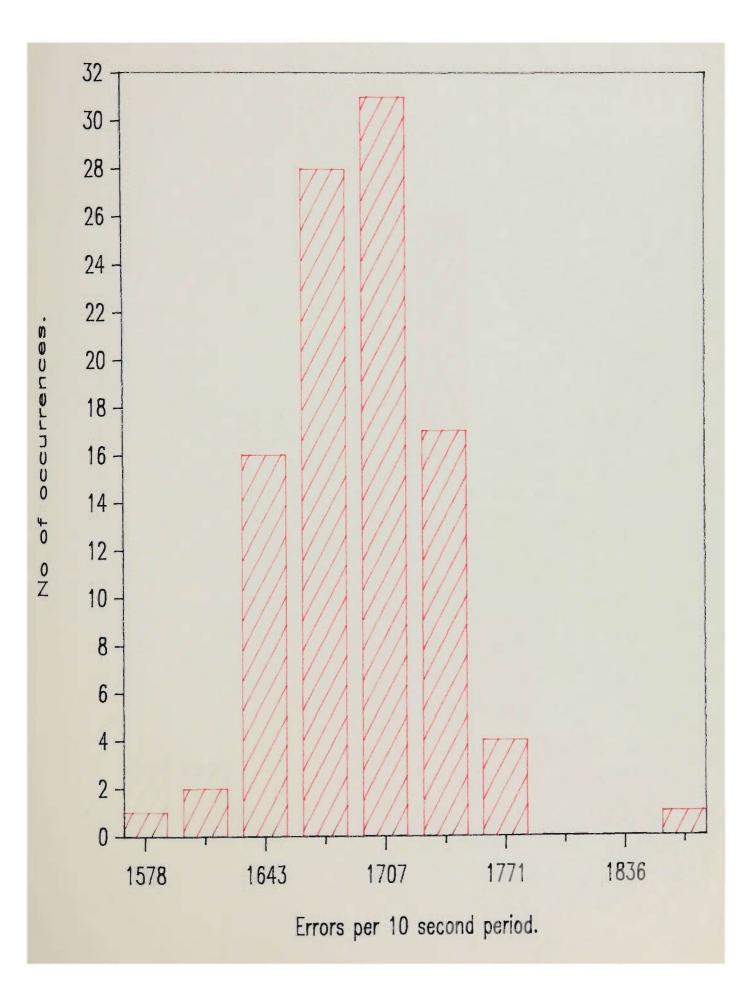

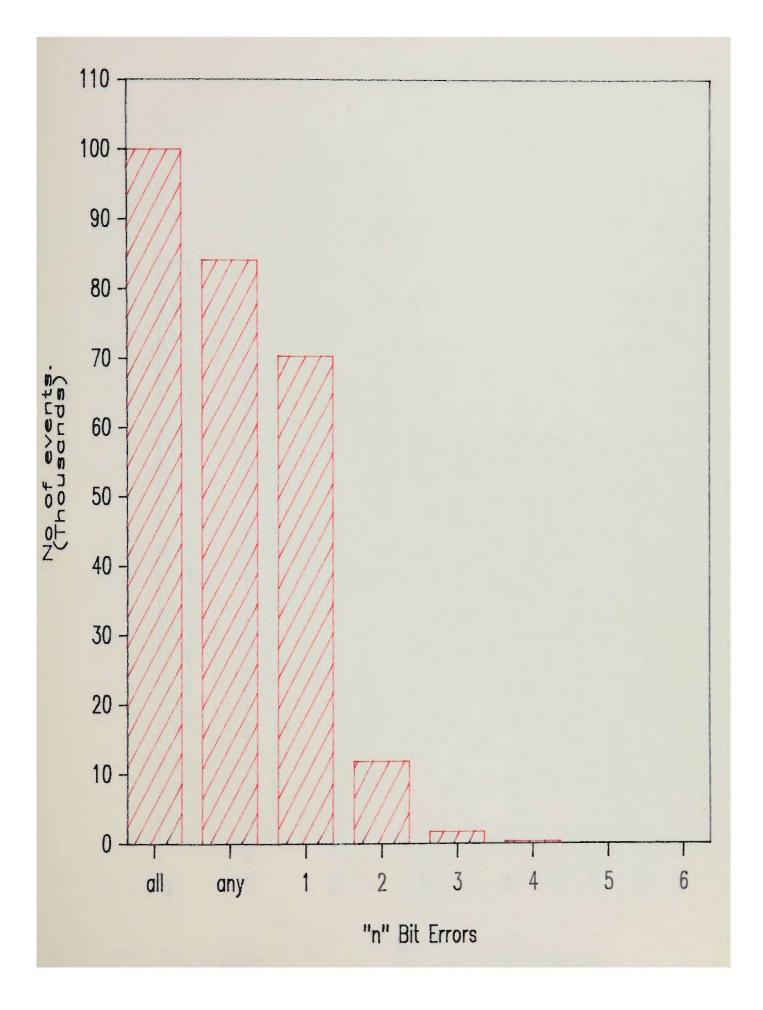

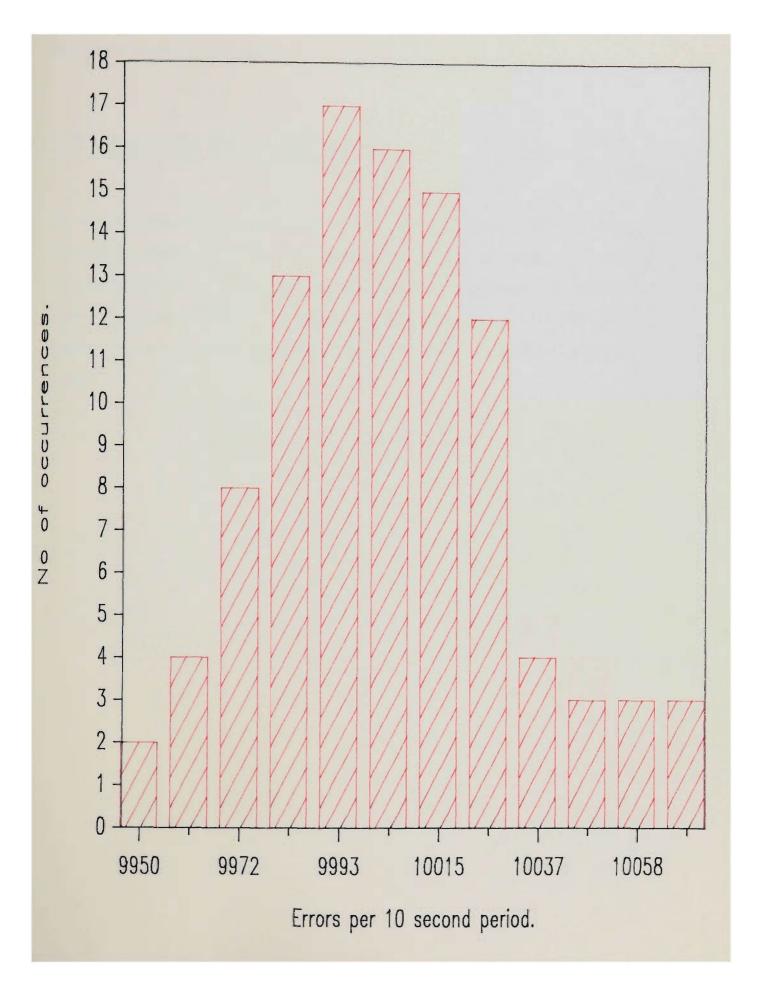

| B7     | Distribution of All Errors (A). $F = 1MHz$ . $R = 1$ in 10           | 171  |

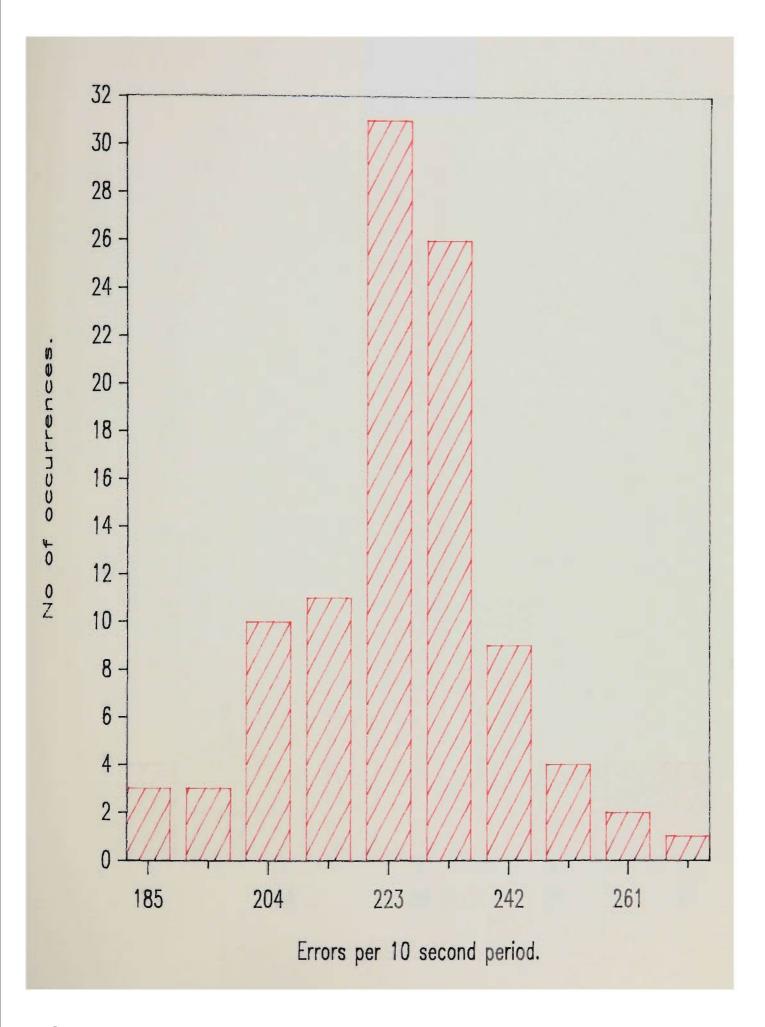

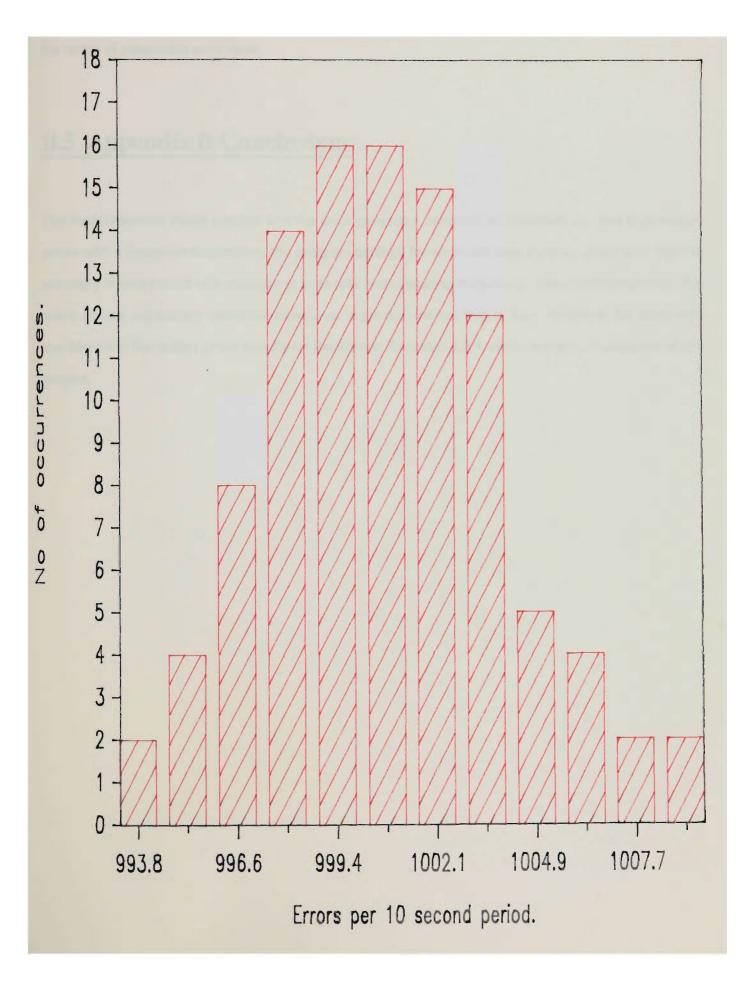

| B8     | Distribution of Any Error (B). $F = 1MHz$ . $R = 1$ in 10            | 174  |

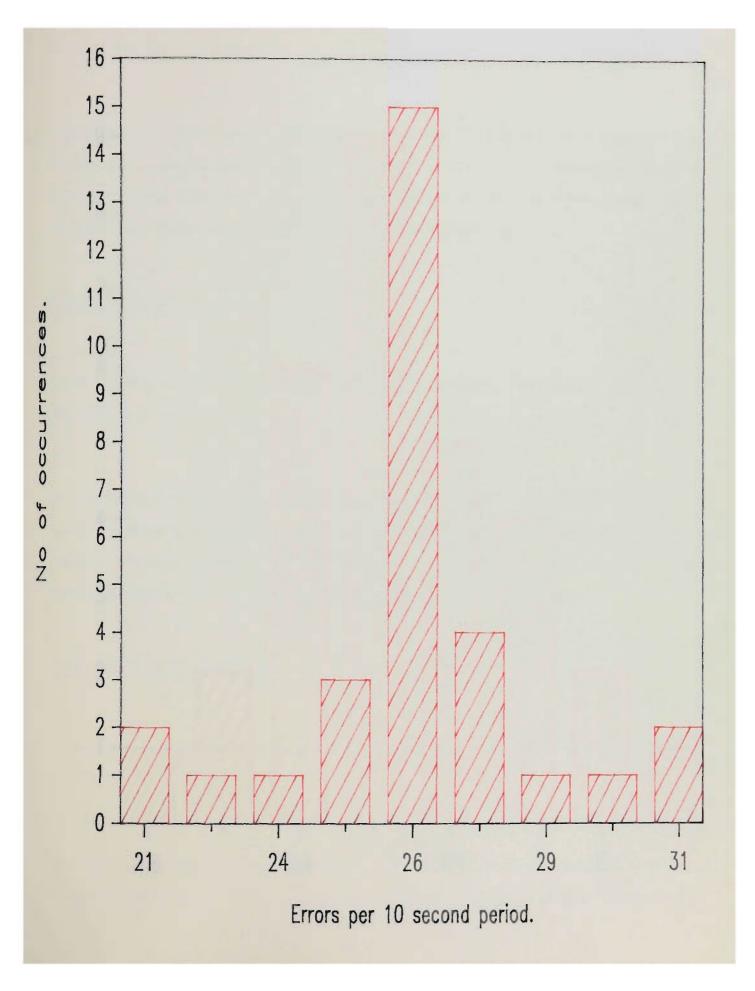

| B9     | Distribution of 1 Bit Errors (C). $F = 1MHz$ . $R = 1$ in 10         | 176  |

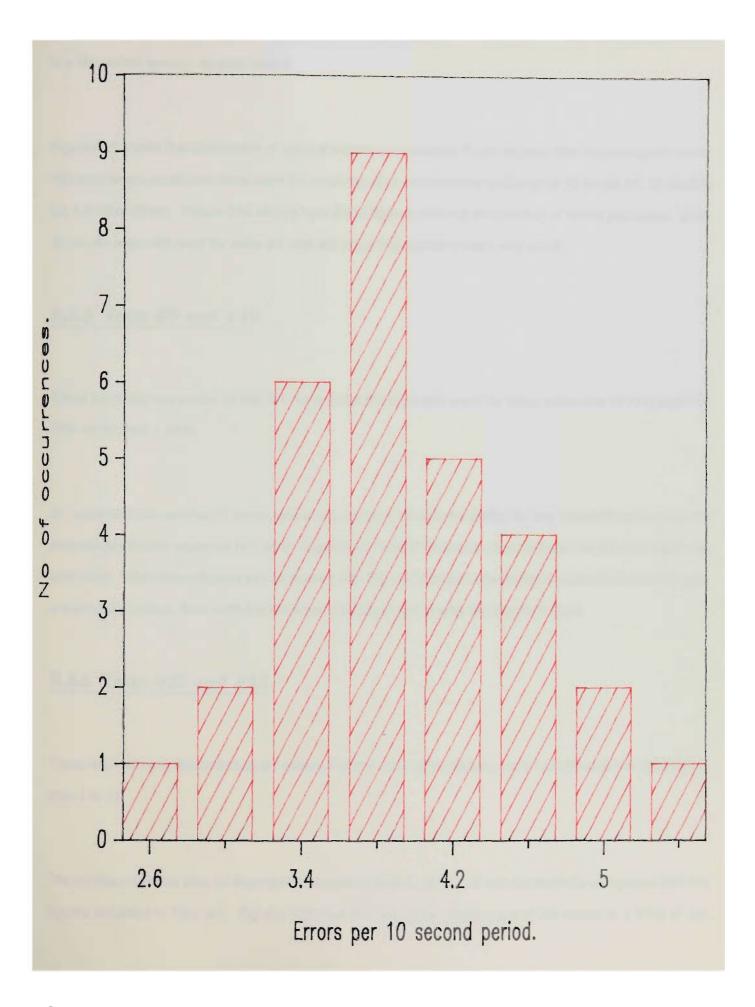

| B10    | Distribution of 2 Bit Errors (D). $F = 1MHz$ . $R = 1$ in 10         | 177  |

| B11    | Distribution of 3 Bit Errors (E). $F = 1MHz$ . $R = 1$ in 10         | 178  |

| B12    | Distribution of 4 Bit Errors (F). $F = 1MHz$ . $R = 1$ in 10         | 179  |

| B13    | Distribution of 5 Bit Errors (G). $F = 1MHz$ . $R = 1$ in 10         | 180  |

| B14    | Distribution of 6 Bit Errors (H). $F = 1MHz$ . $R = 1$ in 10         | 181  |

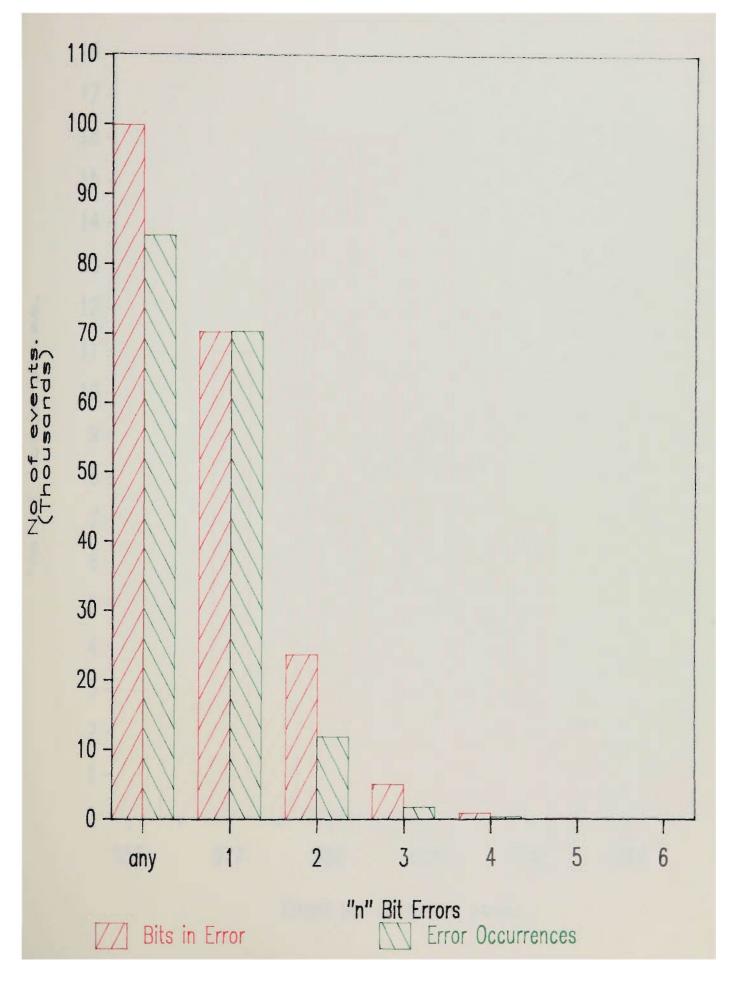

| B15    | Distribution of Separate Error Occurrences                           | 183  |

| B16    | Multi-Bit Error Characteristics                                      | 184  |

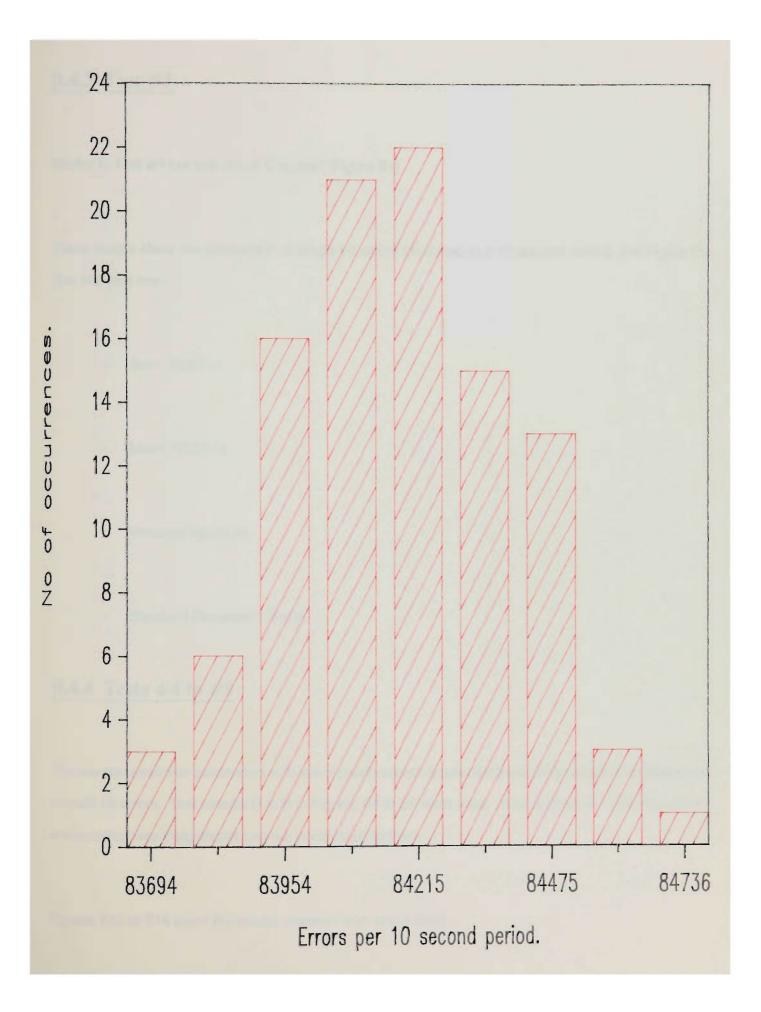

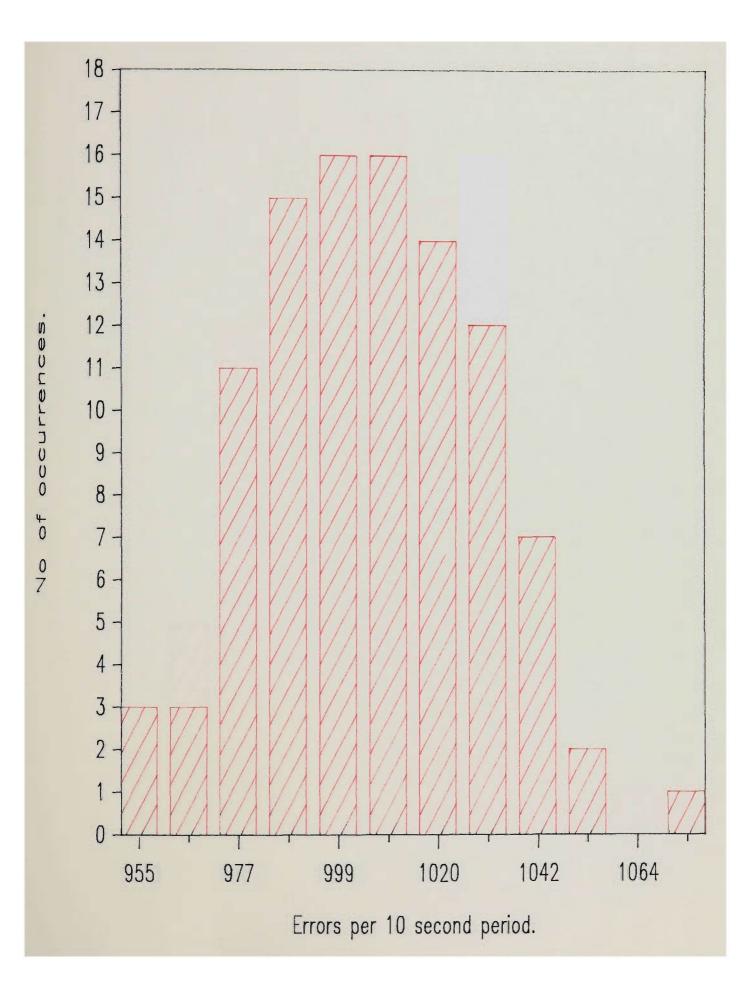

| B17    | Distribution of All Errors (A). $F = 10$ KHz. $R = 1$ in 10          | 185  |

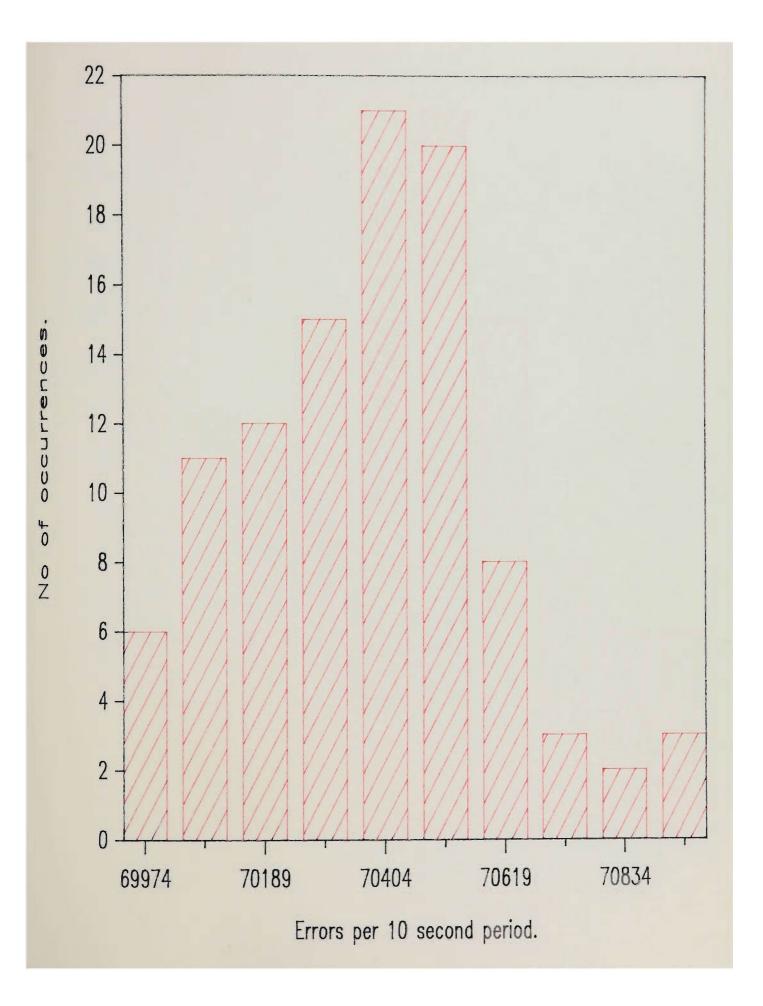

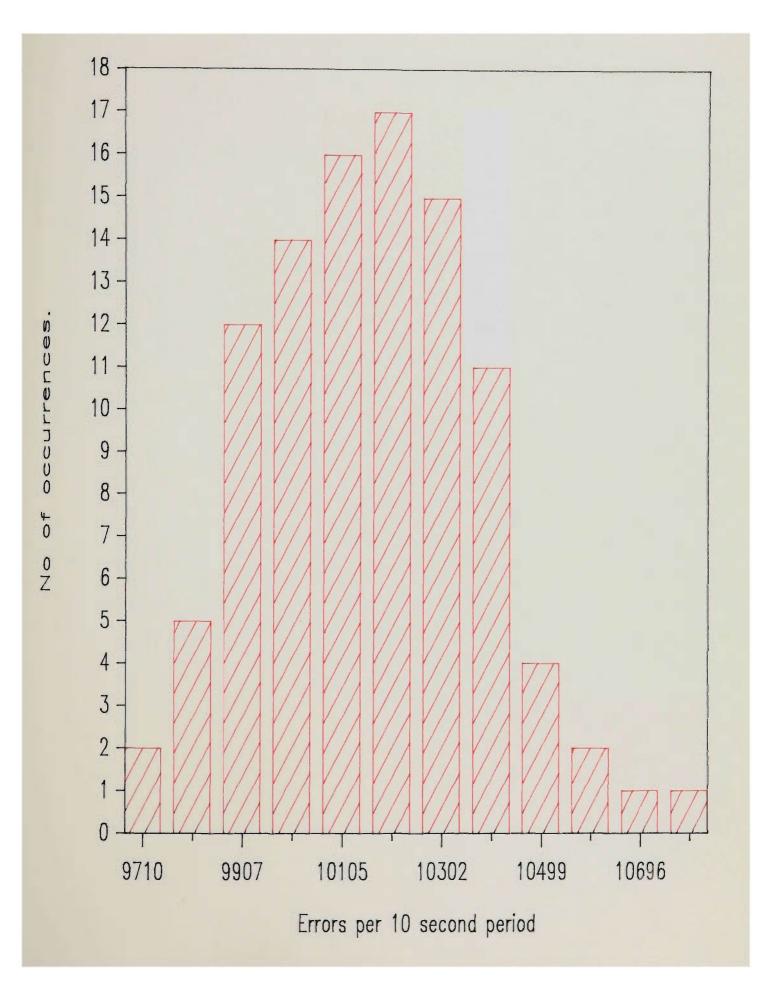

| B18    | Distribution of All Errors (A). $F = 100$ KHz. $R = 1$ in 10         | 186  |

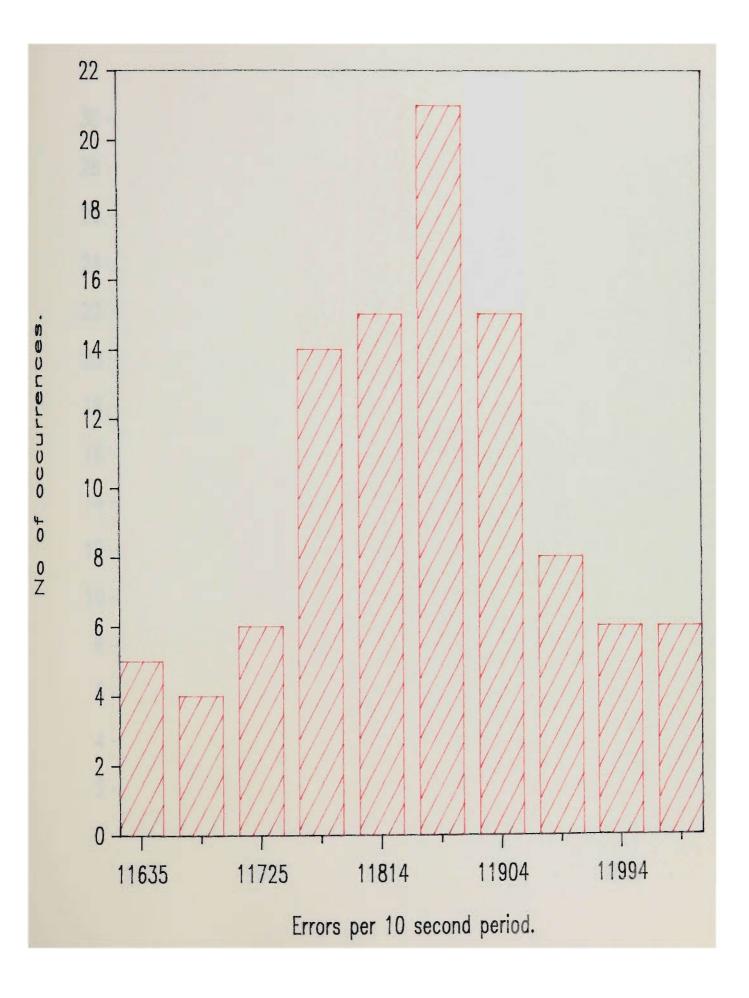

| B19    | Distribution of All Errors (A). $F = 1MHz$ . $R = 1$ in 100          | 187  |

| B20    | Distribution of All Errors (A). $F = 1MHz$ . $R = 1$ in 1000         | 188  |

| Figure | Title                                                      | Page |

|--------|------------------------------------------------------------|------|

|        | · ·                                                        |      |

| C1     | Circuit Schematic of the Analogue Multiplier               | 192  |

| C2     | Internal Schematic of the RS1495                           | 193  |

|        |                                                            |      |

| F1     | Probability Distribution Normal (Gaussian) Characteristics | 235  |

| F2     | Probability Distribution Poisson Characteristics           | 236  |

## **List of Tables**

| Table | Title                                                       | Page |

|-------|-------------------------------------------------------------|------|

|       |                                                             |      |

| 1     | System Timing and Delays                                    | 40   |

| 2     | Peak Throughput as a Function of Vulnerable Period          | 108  |

| 3     | Peak Throughput as a Function of System Model               | 110  |

| 4     | Simulated and Theoretical Throughput Figures                | 112  |

| 5     | Measured Peak Throughput - no interference                  | 128  |

| 6     | Measured Throughput - with interference                     | 132  |

| 7     | Alternative Protocol Throughput - short re-scheduling delay | 135  |

|       |                                                             |      |

| B1    | Error Generator PROM Details                                | 164  |

| B2    | Error Generator Board 1 - Chip List                         | 165  |

| B3    | Error Generator Board 2 - Chip List                         | 166  |

| B4    | Error Generator Test Circuit Definitions                    | 172  |

# Acknowledgements

This research project was supported by a grant from the Australian Telecommunications and Electronics Research Board (ATERB).

The project was supervised by Dr. C. naRanong and Mr. P. Leung, for whose advice and support I am grateful.

My warm thanks are extended to many people, in particular:-

- + My wife, Moira, for typing this thesis

- + My friends and colleagues at F.I.T., for their help and encouragement

- + Mr. F. Hayward, for laying-out the printed circuit boards

- Mr. R. Ives, Mr. M. Dow, Mr. M. Faulkner and Mr. J. MacLeod, for their many informative discussions

- + Dr. R. Malyniak and Dr. A. Kalam for their support, proof reading and criticism of this thesis.

## Abstract

Local Area Networks (LANs) have become fairly common in recent years. This thesis considers the application of Spread Spectrum (SS) communication techniques to the implementation of a LAN.

Basic SS techniques are described and a model of a LAN using these techniques is developed. The major difference between this LAN and most other LAN implementations is that in this system many nodes (or stations) may transmit concurrently. The primary feature of this model is the ability to distinguish between transmissions intended for different users by the address code used to modulate the data. This is called Code Division Multiple Access (CDMA). The properties of the codes, allocated to each node in the network, are of paramount importance in a CDMA system. Several code allocation schemes are considered in order to find one with the most suitable properties. System timing and synchronisation concepts are also considered, since they, together with the code allocation scheme selected, determine the characteristics of the system.

The hardware designed to implement and control network functions is described. Tests carried out to verify the operation of the independent hardware modules are also detailed. The ability of the system to synchronise and transmit data in the presence of noise is tested, prior to complete system testing and throughput measurement.

CDMA is used to separate information on different channels but there is still the need to consider possible contention within a channel. A Carrier Sense Multiple Access with Collision Detection (CSMA/CD) mechanism is used for this purpose. A theoretical model of a suitable mechanism is developed and simulated. The theoretical and simulated results are compared and used to predict the results expected from the hardware. Finally the system's traffic handling characteristics are tested and the results compared with those predicted. System flexibility is investigated by programming an alternative protocol into each node and again examining the throughput characteristics.

This thesis concludes with a discussion of the major features highlighted by this development project. Theoretical, simulated and actual measured results are also compared. Cost and certain system performance parameters are compared with those of a more conventional CSMA/CD network, such as Ethernet. Possible system enhancements and avenues for future work are then discussed.

# **1 INTRODUCTION**

## **1.1 Summary**

This thesis contains the description of the research carried out towards the production of a Local Area Network (LAN) based on Spread Spectrum (SS) techniques [1]. The concept of using Spread Spectrum techniques is attractive since simultaneous transmissions by several users is possible, using a Code Division Multiple Access (CDMA) mechanism.

The evolution of the requirement, a brief introduction to the essential theory and a precis of the contemporary Spread Spectrum LAN research projects are all outlined in chapter 1. An outline of the project design criteria and system specifications are included in chapter 2. The choice of code generation and distribution is crucial to the performance of a CDMA system. Chapter 3 briefly outlines the different coding schemes considered before a final choice was made. After considering several schemes, a synchronised system was adopted as an appropriate code allocation scheme. Timing and code related matters are inseperable in a synchronised system; because of this, aspects of code recognition and collision detection and certain system timing concepts are also described in chapter 3.

Chapter 4 describes the hardware required to generate the codes and meet the timing requirements etc outlined in previous chapter. Photographs of the two printed circuit boards are also included to aid description. Where individual circuit modules have been tested in isolation the tests descriptions are included with the details of the hardware of that particular module. Multi-module and integration tests are, however, detailed separately in chapter 5. Since the hardware is described in terms of the individual circuit modules the complete circuit diagrams, for each of the two boards which constitute a system node, are included in appendices rather than the main section of the text.

The hardware described in chapters 4 and 5 represents the physical components of the system; it is the software which controls the hardware, however, in which the higher level system protocols are embedded. Theoretical and simulation models of channel throughput were developed in order to predict system performance before the control software was written. These models are described in chapter 6. The control software and the tests carried out to verify system performance parameters are described in chapter 7.

A discussion of system performance parameters and ideas for further research are included with an overall evaluation of the research project in the conclusions section, chapter 8.

The aim of this thesis is to describe the main points of the research carried out towards the development of a Spread Spectrum LAN. For this reason all of the control, test and peripheral programs which were written are included as appendices rather than in the main body of the text. Details of special purpose test equipment, photographs of the circuit boards and complete circuit diagrams are also included as appendices.

## 1.2 The Emergence of Local Area Networks

The advent of the microprocessor has had a significant impact on society. The substantial reduction in the cost of computing power has resulted in the widescale use of computers for all kinds of data manipulation and storage. Magnetic storage devices such as floppy disks have, to some extent, replaced paper as a means of intra and inter company data transfer. Local Area Networks (LANs) were primarily developed to allow the sharing of expensive resources, but their development has also allowed the sharing of data between interested parties without the need to manually transport disks, paper tapes etc. The expanding need for data communication channels in LANs has increased the pressure on the available transmission bandwidth. This has led to developments in two broad areas : the extension of the usable spectrum through the use of even higher frequency carriers and the development of complex networking and multiple access algorithms.

The ever increasing use of LANs has brought with it two problems with respect to the protection of data. First it is necessary to protect the data against interference, be it deliberate or otherwise, in order to ensure delivery of correct information to the correct user. Second, as more proprietory information is appearing on data bases, it is becoming increasingly necessary to protect the information against prying or interception. Society has, indeed, become information conscious to the extent that the acquisition and protection of data has become an industry in its own right.

SS techniques, which were originally developed in the mid 1950s [2] for military use as a means of providing a jam resistant communication link, have only recently been considered seriously in a commercial or civilian environment [3]. Areas of interest include mobile radio, radio telephony, amateur radio and satellite communications [4].

## **1.3 Spread Spectrum in LANs**

The adaptation of SS techniques to the development of a LAN appears to offer some advantages in the areas of concern mentioned above. Its well known interference rejection capabilities [5] could be used to advantage in allowing the system to work in an environment where electrical interference might be a problem and where the use of alternatives such as fibre optic cables might not be appropriate[6,7]. SS systems, by their very nature, also offer possible benefits [2,8,9] in the area of data privacy.

One definition of SS [5] which adequately reflects the major characteristics of this technique is as follows:-

"Spread Spectrum is a means of transmission in which the signal occupies a bandwidth in excess of the minimum necessary to send the information. The band spreading is accomplished by means of a code which is independent of the data. A synchronised version of the same code is then used at the receiver in order to despread the signal and facilitate data recovery."

What this definition means is that the data is modulated with the spreading code and that, through a correlation process, the receiver restores the signal to its normal bandwidth and, in doing so, it enhances the desired signal while substantially reducing the effects of interference and noise. Overall, the communication channel capacity is not "wasted" because with a suitable selection of spreading codes (having low crosscorrelation properties) several nodes may simultaneously transmit messages over the same channel, with low, predictable, interference between nodes.

A LAN, where multiple nodes use a single communication channel - one pair at a time, is a prime candidate for the application of SS techniques. By using CDMA techniques, alternatively called Spread Spectrum Multiple Access (SSMA), it is possible to have several multi-pair communications in progress simultaneously [10,11]. Being inherently multi-user, CDMA techniques have the potential to increase the network's throughput, under conditions of heavy usage, by allowing many pairs of nodes to communicate simultaneously, thus reducing contentions.

The three primary methods of spreading the data transmissions are [5,12]:-

- Direct Sequence in which the data is directly modulated with a fast pseudo random code sequence.

- Frequency Hopping in which the carrier which is modulating the data is caused to hop from one frequency to another in a pseudo random manner.

Time Hopping - in which the time channel allocated to a particular transmission is changed in a pseudo random manner.

## **1.4 Literature Survey and Existing Systems**

A survey of literature revealed many papers on Spread Spectrum techniques and many more on Local Area Networks, but only four papers which described research which combined both [13 - 16]. Several more papers relating to one of the four existing research projects were published subsequently. These papers described the project at various stages of its development, the most recent [17] was used as a reference. The projects described were at various stages of completion, varying from systems which had been extensively tested to those which had been simulated, but for which no hardware had been built.

The characteristics of each system in brief are as follows:-

#### 1.4.1 System A [13 and 17]

Smythe and Spracklen [13] describe their SS LAN system, and the software simulations used to test it, in general terms. Spracklen et. al. [17], however, give a much more comprehensive description of the system. The system, called SPREADNET, is a bus topology system which is connected via fibre optics, and is aimed specifically towards military applications. In this network, which can be up to 2 km. in length, as many as 150 users can be accommodated. Direct sequence modulation is used and encoded data is transmitted in baseband at 100 M bits/sec. Each node controller uses a 12 MHz MC68000 microprocessor.

A source code address allocation scheme is used, where the receiver must be informed which demodulation code to use. Upon receipt of a packet for transmission the node controller requests a virtual communications channel ie. requests address codes to be used for the transmission. The management

system then informs the transmitter and receiver of the choice of codes. Contentions are avoided by this elaborate network management interchange before logical code to physical device mapping is achieved.

All codes allocated in this manner are encrypted before delivery and are protected by a two key cryptographic algorithm in conjunction with the Data Encryption Standard (DES). Dynamically allocated codes are also used by the individual node controllers to transmit network management information around the system.

Synchronisation is achieved by means of polarity coincidence correlators, and digital correlation is performed continuously to overcome tracking problems. Modulation and demodulation are handled by dedicated hardware (custom programmed logic arrays), and a sliding correlator is used in conjunction with polarity coincidence correlation for data recovery.

#### 1.4.2 System B [14]

System B was developed, to investigate network efficiency and performance criteria and compare them with the classic Frequency Division Multiple Access (FDMA) ALOHA type of network. The system is cable connected, and used "uplink" and "downlink" separation of transmission and reception paths interfaced via a "Repeater and Sync generator". Bus topology and direct sequence (DS) modulation are used. Bit synchronisation is achieved via a sophisticated mechanism whereby the Repeater and Sync generator periodically interrupts traffic to inject sync information for each user. This must be done with sufficient frequency so that the local clocks do not drift by more than one chip bit period between updates.

The system is designed to accommodate voice and data. Voice or data bits are transmitted in packets. Different processing gains are used in the system, and data is modulated using a variable number, between 64 and 512, of chip bits per data bit, whereas a processing gain of 167 is used for voice traffic. This gives an effective modulated data rate of 10.9 MHz for voice traffic of 64 kHz. Bits of each packet, either voice or data, are modulo 2 added to the direct address code sequence. The resulting binary array then balance modulates a high frequency carrier which is transmitted in the uplink direction. The Multiple Access protocol is via point to point CDMA, with the destination address being used, but no code allocation details are included.

#### 1.4.3 System C [15]

This system utilises what the designers call "a non-processed fibre optics bus", where non-processed is defined as supressing the entire command and address part of the bus. A distributed star topology is used to implement the bus, which is capable of supporting up to 25 users. Distributed 5 port optical couplers are used to allow a bus do be developed which does not use handshaking or a master-slave configuration.

Fibre optic interconnections are used and modulation takes the form of Frequency Hopping superimposed upon a Direct Sequence modulated data signal. 15 frequencies with a separation of 15 MHz centred on 155 MHz are used for the frequency hopping component, and a processing gain of 127 is used for the direct sequence part. Surface wave acoustic convolvers centred on 155 MHz are used for synchronisation.

#### 1.4.4 System D [16]

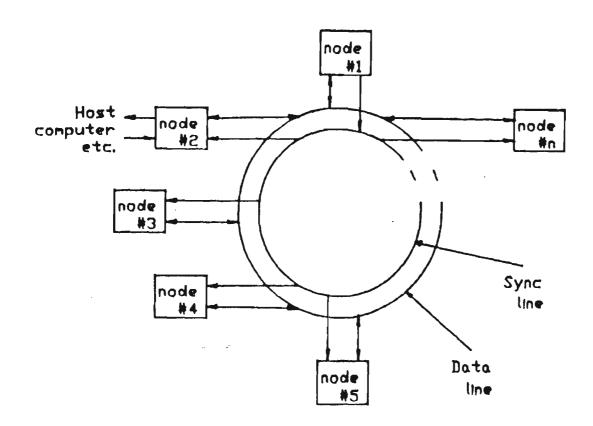

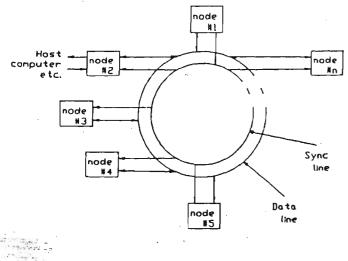

For this system a fibre optic connected ring network and a separate synchronisation bus are used. Both synchronous and asynchronous data is catered for in the system.Node addresses are cyclically bit shifted versions of the one m-sequence. The sync signal sent from the Sync Node is also a bit shifted m-sequence. The system employs dual phase locked loops for synshronisation demodulation and data separation.

Each receiver removes its own modulated data signal from the received signal, so node #2 would see the same signal as node #1 minus any transmission addressed to node #1. This prevents the transmission for node #1 from recirculating in the system. Each node conducts an "in-channel" busy test before transmitting. When a node is transmitting it switches its receiver and transmitter m-sequence generators to the destination address. This ensures that no collisions can occur in that channel as the node would remove from any signal any component modulated with the same address code. It does, however, mean that a node may not transmit and receive at the same time.

The research described in these papers appeared to be concentrating on the high speed, extremely sophisticated end of possible applications. Considerable use was made of custom designed VLSI devices, multiple high speed correlators etc. Network management, sophisticated synchronisation, layered SS techniques, encryption and dynamic address code allocation were some of the other advanced features of the systems referenced. Three of the systems used, or proposed using, fibre optic interconnections and only one used cables. This concentration on the "high end" of possible applications left considerable scope for the development of a SS LAN which could find applications where the advanced features described above might not be appropriate (see System Specifications, section 2.4) and systems such as those described above may be too complicated.

### 1.5 Autocorrelation, Crosscorrelation and Orthogonality

The correlation between two signals gives an indication of the similarity between the signals, as a function of the time displacement ( $\tau$ ). The **crosscorrelation** between two signals **v(t)** and **w(t)** is defined by the scalar product shown below [18]

$$R \vee w(\tau) = \langle \vee(t), w(t - \tau) \rangle$$

<sup>(1)</sup>

Thus, if the correlation value is high the signals have a marked degree of similarity; and if the correlation value is very low the signals are essentially dissimilar. The **autocorrelation** function is defined as the correlation of a signal v(t) with a time displaced version of itself  $v(t-\tau)$  and is given by:-

$$\mathbf{R}\mathbf{v}\mathbf{v}(\tau) = \mathbf{R}\mathbf{v}(\tau) = \langle \mathbf{v}(t), \mathbf{v}(t-\tau) \rangle$$

(2)

If  $|\mathbf{Rv}(\tau)|$  is large then the inference is that  $\mathbf{v}(t)$  is very similar (proportional) to  $\pm \mathbf{v}(t)$  for that particular value of  $\tau$ . Conversely if  $\mathbf{Rv}(\tau) = \mathbf{0}$  then, at that particular value of  $\tau$ ,  $\mathbf{v}(t)$  and  $\mathbf{v}(t-\tau)$  are said to be **orthogonal**.

For a signal z(t) which is a summation of two signals v(t) and w(t), such that z(t) = v(t) + w(t), the correlation with one signal v(t) would be given by

$$Rzv(\tau) = Rv(\tau) + Rwv(\tau)$$

(3)

and if the component signals are orthogonal at this particular value of  $\boldsymbol{\tau}$  ie. if

$$\mathbf{R} \vee \mathbf{w}(\tau) = \mathbf{R} \mathbf{w} \vee (\tau) = \mathbf{0} \tag{4}$$

then

$$Rzv(\tau) = Rv(\tau)$$

This extraction of a single correlation function from a signal which is the summation of two or more signals is the basis upon which CDMA relies.

### 1.6 Features Required in CDMA Codes

In a CDMA system where one node is distinguished from another by means of the code used to modulate its data, the selection and allocation of codes is of prime importance. The address codes used must have certain properties [5,8] i.e. they:-

- i) must be easy to generate.

- ii) have randomness properties.

- iii) have selectable length (long) periods.

- iv) must be deterministic i.e. can be synchronised.

- v) must be orthogonal

and if the code is intended to impart any substantial degree of encryption they must also be:-

vi) difficult to reconstruct from a short segment.

It can be seen that properties i), iv) and vi) are somewhat contradictory since, if it is simple, deterministic and easy to synchronise for the intended receiver, it will probably prove to be relatively easy for an interceptor to "**break**" the code. Since, however, cryptographic integrity is not a primary requisite of this work, property vi) may be omitted thus opening the way to use codes which have only the first five properties.

#### **1.7 Maximal Length Sequences**

The most commonly used type of code which meets these five basic properties is the Maximal Length Sequence (MLS or m-sequence). The normal method of generating these codes is using Linear Feedback Shift Registers (LFSR) as illustrated in Figure 1a. For a code to be a maximal length code it must have a length, N, which is equal to  $2^{n}$ -1, where n is the number of shift register stages in the generator. Tables are available [19] which show the feedback taps necessary to generate m-sequences for up to 34 shift register stages. In an m-sequence all binary n-tuples, except the all zero state, are present. By setting the initial contents of the shift registers to 0001 the pattern shown as code C<sub>x</sub> in Figure 1b would result. This pattern repeats after  $2^{4}$ -1 = 15 bits. Figure 1b also shows code C<sub>y</sub> which is the result of cyclically shifting code C<sub>x</sub> by 1 bit such that C<sub>xk</sub> = C<sub>yk-1</sub> where k represents the bit position.

The signals v(t) and w(t) in section 1.5 were continuous signals. The autocorrelation and crosscorrelation functions do, however, have a direct translation into discrete pseudo random signals such as m-sequences. By defining the  $\pm 1$  sequence  $C_{x'k} = 1-2C_{xk}$  (where  $C_{xk} = 0,1$  - see Figure 1b) then the autocorrelation function is defined as

$$RCx'(\tau) = \sum_{1}^{N} Cx'_{k} Cx'_{k-\tau}$$

(6)

This is the **Periodic Autocorrelation** of the m-sequence taken over the length, **N**, of the sequence, and  $\tau$  is in whole bit increments. [5]

The Periodic Crosscorrelation of two sequences Cx' and Cy' would similarly be given by

$$RCx'Cy' = \sum_{1}^{N} Cx'_{k}Cy'_{k}$$

(7)

which is a bit by bit summation of the number of bits in code  $C_x$ ' which are the same as those in code  $C_y$ ' over the length, N, of the codes. The periodic autocorrelation and crosscorrelation functions are of extreme importance when considering SS systems.

#### **1.8 Basic Spread Spectrum Theory**

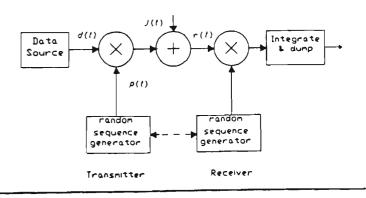

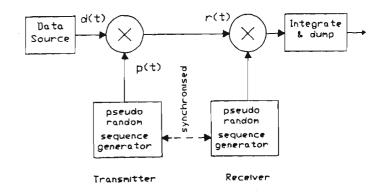

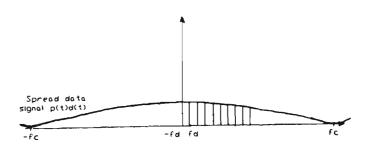

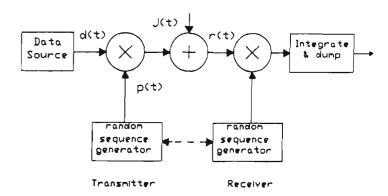

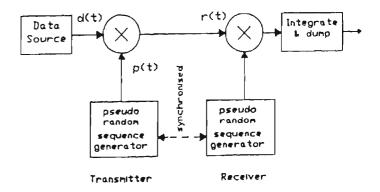

This research project uses the Direct Sequence method of data spreading, and the description will concentrate on this aspect. The pseudo random binary sequence used to spread the data is also commonly known as the "**Chip**" sequence. Figure 2 illustrates a conceptual model of a single channel direct sequence system. In this system the chip sequence is used directly to modulate the data in baseband.

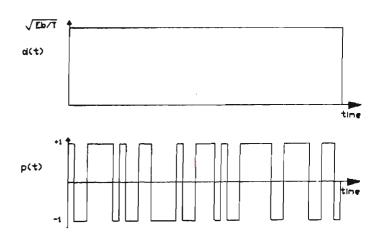

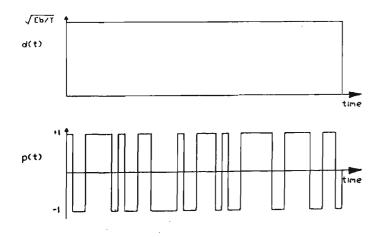

Each data bit d(t), as illustrated in Figure 3, of energy Eb and duration T, may be represented by [5]

$$d(t) = \pm \sqrt{(E_b/T)}$$

(8)

Figure 2 Single Channel Direct Sequence System

This one dimensional data bit is multiplied by a two level  $\pm 1$  chip sequence, C'(t), running at a frequency of  $f_c$  chips/sec, ie. a total of  $f_c$ T chips per data bit. The resultant sequence d(t)C'(t) is then a  $f_c$ T dimensional signal. The relationship between the data and chip signals is shown in Figure 3

The ratio of the dimensionality of the chip sequence to the data is called the "Processing Gain", and is defined as :-

Processing Gain =

$$G_p = \underline{Bss}_{BD}$$

(9)

Where  $B_{SS} = Bandwidth$  of the SS Signal and  $B_D = Bandwidth$  of the Data Signal

The numerical value of the processing gain is an indication of a power improvement factor, which a receiver, possessing a copy of the transmitter's chip sequence, can achieve by a process of correlation. The processing gain gives an indication of the interference rejection capability [5].

If the "chipped data" signal, d(t)C'(t), is transmitted in the presence of an interfering signal J(t), the received signal would be

$$r(t) = d(t)C'(t) + J(t)$$

$0 \le t \le T$  (10)

At the receiver the correlation process is carried out by multiplying the received signal, r(t), with the same chip sequence used to encode the transmitted data, and then integrating the result over a period T to produce a decision variable U, where

$$U = \sqrt{(E_b/T)} \int_0^T r(t)C'(t) dt$$

(11)

From equation (11) it can be determined whether  $+\sqrt{(E_b/T)}$  or  $-\sqrt{(E_b/T)}$  was sent, depending on whether **U** is positive or negative. The integrand in equation (11) may then be expanded as follows

$$r(t)C(t) = d(t)C'^{2}(t) + J(t)C'(t)$$

(12)

And, since C'(t) =  $\pm 1$  ( $\therefore$  C'<sup>2</sup>(t) = 1), the above equation may be rewritten as

$$r(t)C'(t) = d(t) + J(t)C'(t)$$

(13)

With suitable filtering the high frequency component J(t)C'(t) may be removed and the original data signal, d(t), recovered.

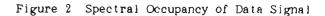

This fact can be illustrated by inspection of the the spectral occupancy of the signals shown in Figure 4, where the power spectral densities of the data signal, d(t), and the spread data signal, d(t)C'(t), are sketched. The data signal may be extracted by using a filter with a bandwidth of  $f_d$  Hz. The fraction of power due to the interfering signal which can pass through this filter is then  $1/f_cT$ . Thus the data can have an effective power advantage over the interfering signal of  $n = f_cT$ , i.e. the processing gain, defined in equation (9) above.

Figure 4 Spectral Occupancy of Signals

In equation (13) the jamming signal J(t) may be an external interference signal, eg. nearby high voltage equipment, and/or it may be interference from other transmitting nodes. The rejection of the other nodes transmissions as noise depends upon the orthogonality of the codes [20] used for spreading each node's data.

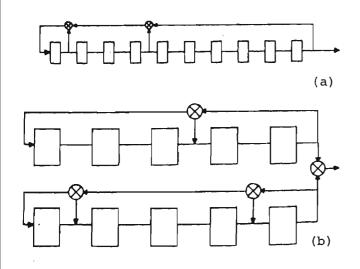

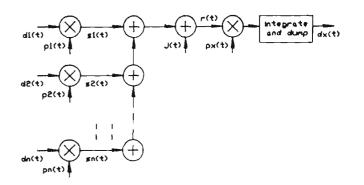

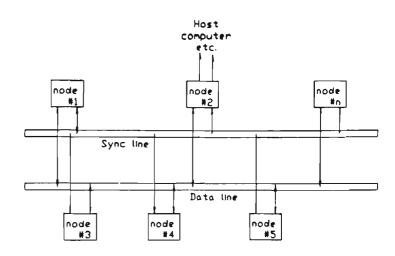

### **1.9 Multiple Access in a Spread Spectrum System**

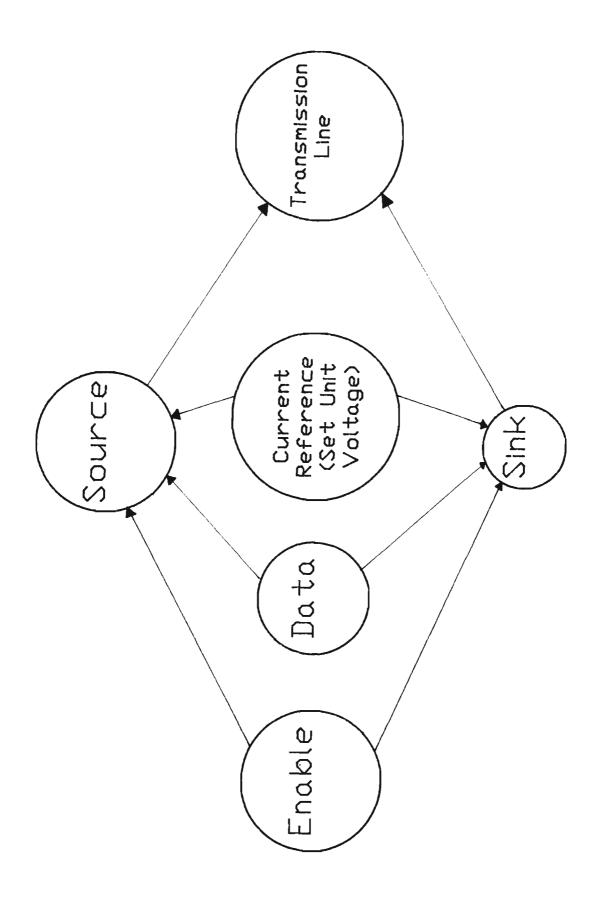

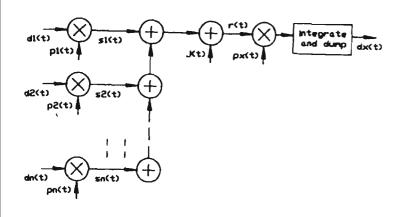

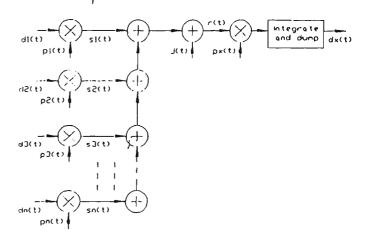

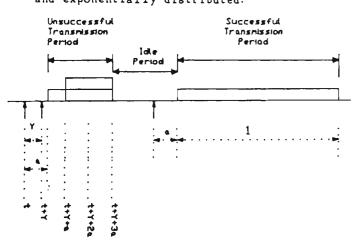

The concept of simultaneous multi-access is illustrated in Figure 5. This diagram shows a number of transmitting nodes (n) and a single receiver (node #x) (where  $1 \le x \le n$ ). At each transmitter the data bit,  $d_n(t)$ , is modulated with an address code,  $C_n'(t)$ , to form the output,  $s_n(t)$ , such that

$$s_n(t) = C_n'(t) d_n(t)$$

(14)

The signal from each transmitter is then "**added into**" the transmission medium as illustrated in Figure 6, to produce a total transmission signal **T(t)** of the form

$$T(t) = s_1(t) + s_2(t) + s_3(t) + \dots s_n(t)$$

(15)

$$= \sum_{1}^{n} s_{n}(t)$$

(16)

The transmission medium may be subjected to external noise or interference, J(t), which would then result in a received signal of the form

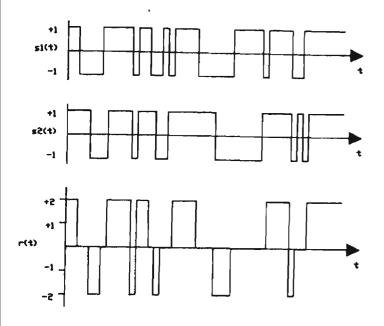

Figure 6 Typical Transmitter Waveforms

$$\mathbf{r}(\mathbf{t}) = \mathbf{T}(\mathbf{t}) + \mathbf{J}(\mathbf{t})$$

At the receiver the received signal, r(t), is demodulated by multiplying with the address code for that node,  $C_x'(t)$ , and, from equation (11)

$$r(t)C_{x}'(t) = d_{x}(t) + \sum_{1}^{x-1} s_{n}(t)C_{x}'(t) + \sum_{x+1}^{n} s_{n}(t)C_{x}'(t) + J(t)C_{x}'(t)$$

(18)

By suitable filtering the data signal,  $d_x(t)$ , may be extracted from all of the other components indicated in equation (18). In this manner any receiver may extract its own data from all of the other signals which have been simultaneously combined onto the network, ie. the receiver may access its own data by using CDMA.

# **2 OUTLINE OF THE RESEARCH**

# 2.1 Summary

Chapter 2 outlines the aims of this research project and the the breakdown of the overall task into smaller packages with identifiable milestones. A brief description of the potential advantages of SS technology in a network situation is then given. Finally, the system's network specifications are detailed.

## 2.2 Design Aims

The primary aim of this research is to produce a LAN using SS techniques, and to evaluate some of the performance parameters of the system produced. The project should use either twisted pair or parallel pair cables as the interconnection medium in order to maintain the simplicity of the design. The overall network should use standard, off the shelf, components wherever possible.

In order to satisfy these requirements the research was divided into separate sections :-

- Selection of appropriate coding sequences.

- Development of timing, synchronisation and decoding philosophies for these sequences.

- Transmission of a synchronising sequence, and subsequent clock recovery.

- Development of a driving technique suitable to ensure that the connection or disconnection of a station (or a number of stations) would not substantially affect the electrical characteristics of the network.

- Design of data recovery hardware.

- Design of microprocessor control circuit for the system.

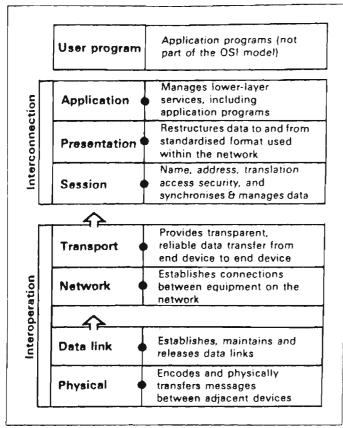

- Investigation into the hardware and software protocol structure to fulfil the requirements of the lower levels of the International Standards Organisation (ISO) seven layer model.

- Demonstration of concurrent transmissions.

# 2.3 Spread Spectrum vs Current Networks

Current bus and ring LAN topologies typified by Ethernet and Cambridge ring [21,22] respectively employ some form of (asynchronous) time division multiplexing. This may be in the (more or less) fixed compartment format of Cambridge Ring or the "packet message" type format of Ethernet. Whichever system is used, any node wishing to access the network must wait until a time when no other users are transmitting. The node will then transmit at a high frequency in the order of 10 MBits/sec into the system. The overall effect is that each node emits bursts of data at high bit rates for relatively short periods, and then remains dormant for a much longer period.