### Power Management Schemes for Ultra Low Power Biomedical Devices

David Fitrio, S.Kom (B.Eng Comp.E), M.Eng EE

Submitted in Fulfilment of the Requirements for The Degree of Doctor of Philosophy

School of Electrical Engineering Faculty of Health, Engineering, and Science Victoria University

> PO Box 14428 Melbourne City MC Victoria, Australia, 8001

"Never look down on anybody unless you are helping them up." --Jesse Jackson

"Everyone who works have some burdens to bear in their lives. Not just you. Still everyone continues working. That's what it means to work for a living."

--Bambino

"People who don't focus on the job in front of them have no right to talk of their dreams."

--Bambino

"The greatest danger for most of us is not that our aim is too high and we miss it, but that is too low and we reach it."

--Michelangelo

# Table of Contents

| DECLARATION OF ORIGINALITY                                                           | I   |

|--------------------------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENT                                                                      | II  |

| LIST OF FIGURES                                                                      | IV  |

| LIST OF TABLES                                                                       | X   |

| LIST OF ABBREVIATIONS                                                                | XI  |

| LIST OF PUBLICATIONS                                                                 | XIV |

| ABSTRACT                                                                             | XVI |

| CHAPTER ONE:                                                                         |     |

| 1.1 BACKGROUND OF THIS RESEARCH<br>1.2 MOTIVATION                                    | 3   |

| 1.3 Research Objectives and Aims<br>1.4 Research Design Methodologies and Techniques |     |

| 1.5 ORIGINALITY OF THE THESIS                                                        |     |

| 1.6 Thesis Organisation                                                              |     |

| CHAPTER TWO:                                                                         | 9   |

| 2.1 HOME CARE SYSTEM                                                                 |     |

| 2.1.1 Introduction                                                                   |     |

| 2.1.2 Medical monitoring Systems                                                     |     |

| 2.1.3 What is being Monitored?<br>2.1.4 Home Tele-care System                        |     |

| 2.1.5 Essential Home Health Care System Building Blocks                              |     |

| 2.1.5.1 Health Sensory and Personal Server                                           |     |

| 2.1.5.2 Telecommunications                                                           |     |

| 2.1.5.3 Medical Service Providers                                                    |     |

| 2.1.5.4 System Design Issues                                                         |     |

| 2.2 CONCLUSION                                                                       | 16  |

| CHAPTER THREE:                                                                       |     |

| 3.1 INTRODUCTION                                                                     |     |

| 3.2 DYNAMIC POWER REDUCTION THROUGH VOLTAGE SCALING                                  | = - |

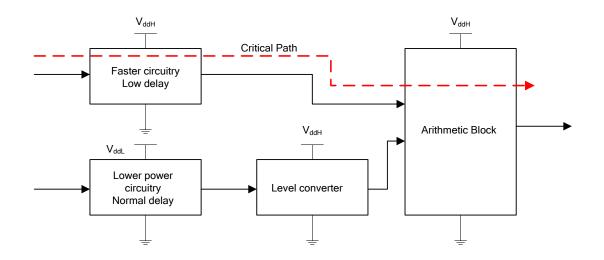

| 3.2.1 Multiple Supply Voltage Scaling                                                |     |

| 3.2.2 Architectural Voltage Scaling                                                  |     |

| 3.3 MOS DRAIN CURRENT MODELLING                                                      |     |

| 3.4 EFFECTS ON LEAKAGE CURRENT                                                       |     |

| 3.4.1 Effective higher threshold voltage biasing schemes to reduce leakage current   |     |

| 3.4.2 Source voltage reverse biasing scheme                                          |     |

| 3.4.3 Gate voltage reverse biasing scheme                                            |     |

| 3.4.4 Bulk/Substrate biasing scheme                                                  |     |

| 3.4.5 Source-gate voltage offset biasing scheme                                      |     |

| 3.4.6 Source-drain voltage reduction scheme                                          |     |

| 3.4.7 Comparison of simulated results for different biasing schemes                  |     |

| 3.4.8 Circuit application techniques of high threshold voltage circuit biasing schemes |     |

|----------------------------------------------------------------------------------------|-----|

| 3.4.8.1 Multi-Threshold CMOS                                                           |     |

| 3.4.8.2 Variable-Threshold CMOS                                                        |     |

| 3.5 CONCLUSION                                                                         | 38  |

| CHAPTER FOUR:                                                                          | 39  |

| 4.1 DC-DC CONVERSION                                                                   | 39  |

| 4.1.1 Introduction                                                                     |     |

| 4.1.2 Types and Challenges of Low Voltage DC-DC Conversion                             |     |

| 4.1.2.1 Low-Voltage High-Current DC-DC Conversion                                      |     |

| 4.1.2.2 Low-Voltage Low-Current DC-DC Converter                                        |     |

| 4.1.3 The Importance of Voltage Regulation                                             |     |

| 4.1.3.1 Circuit connected directly to the battery cell                                 |     |

| 4.1.3.2 Circuits connected to a linear regulator                                       |     |

| 4.1.3.3 Circuits connected to a switching regulator                                    |     |

| 4.1.3.4 Comparisons of the system run-time                                             |     |

| 4.2 Switching Regulators Converter Topologies                                          |     |

| 4.2.1 Buck Converter                                                                   |     |

| 4.2.2 Boost Converter                                                                  |     |

| 4.2.3 Buck-Boost Converter                                                             |     |

| 4.2.4 Converter choice for a low power battery operated system                         |     |

|                                                                                        |     |

| 4.3 CONCLUSION                                                                         |     |

| CHAPTER FIVE:                                                                          | 54  |

| 5.1 INTRODUCTION                                                                       | 54  |

| 5.2 DYNAMIC VOLTAGE SCALING DEFINITION                                                 |     |

| 5.3 DYNAMIC VOLTAGE SCALING DEFINITION                                                 |     |

|                                                                                        |     |

| 5.4 DVS Modules Power Consideration                                                    |     |

| 5.5 DVS MODULES CIRCUIT IMPLEMENTATION                                                 |     |

| 5.5.1 Digital to Analog Converter                                                      |     |

| 5.5.1.1 DAC Types                                                                      |     |

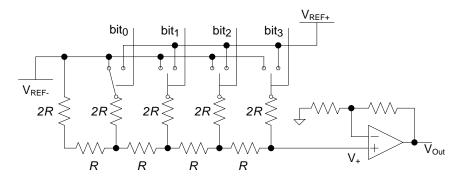

| 5.5.1.1.1 Typical R-2R Resistor Ladder DAC                                             |     |

| 5.5.1.1.2 Voltage Mode Resistor Ladder DAC                                             |     |

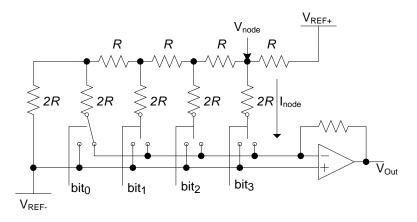

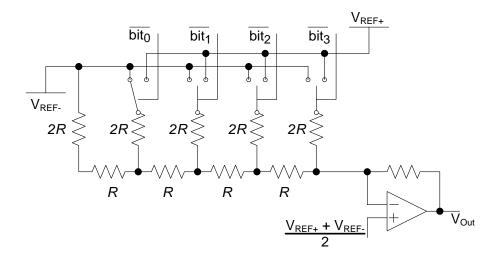

| 5.5.1.1.3 Current Mode Resistor Ladder DAC                                             |     |

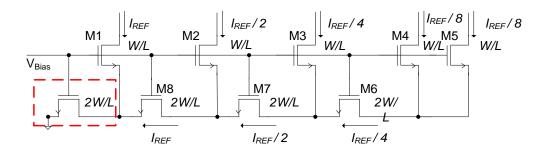

| 5.5.1.1.4 MOS Transistor DAC                                                           |     |

| 5.5.1.2 Improving Linearity in Low Power Weak Inversion DAC                            |     |

| 5.5.1.2.1 Intercorrelation Mismatch Correction Transistor<br>5.5.1.2.2 Voltage Bias    |     |

| 5.5.1.2.3 Transistors Dimension                                                        |     |

| 5.5.1.3 DAC performance                                                                |     |

| 5.5.2 Pulse Width Modulator                                                            |     |

| 5.5.2.1 PWM Design Specifics                                                           |     |

| 5.5.3 Current-Starved Voltage Controlled Oscillator                                    |     |

| 5.5.3.1 Current Starved VCO with selectable frequency                                  |     |

| 5.5.3.2 VCO design specifics                                                           |     |

| 5.5.3.3 Transistor parameter sizing                                                    |     |

| 5.5.4 Phase and Frequency Detector                                                     |     |

| 5.5.5 Buck converter                                                                   |     |

| 5.5.5.1 Buck Converter Design Equations                                                |     |

| 5.5.5.1.1 Derivations for the Duty Ratio                                               |     |

| 5.5.5.1.2 Calculation to determine the value of the Inductor                           |     |

| 5.5.5.1.3 Calculation to determine the value of the Inductor                           |     |

| 5.6 CONCLUSION                                                                         |     |

| CHAPTER SIX:                                                                           |     |

|                                                                                        |     |

| 6.1 INTRODUCTION                                                                       |     |

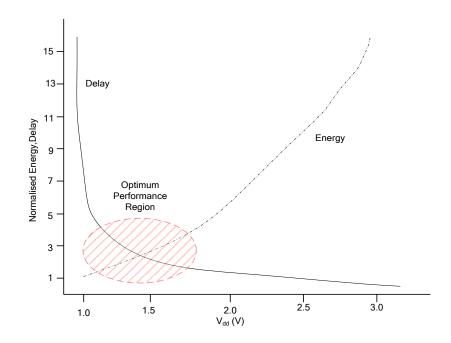

| 6.2 Energy-performance curve for optimal $V_{DD}$ - $V_T$ operation                    |     |

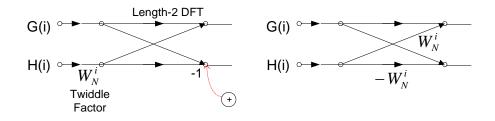

| 6.3 FAST FOURIER TRANSFORM                                                             |     |

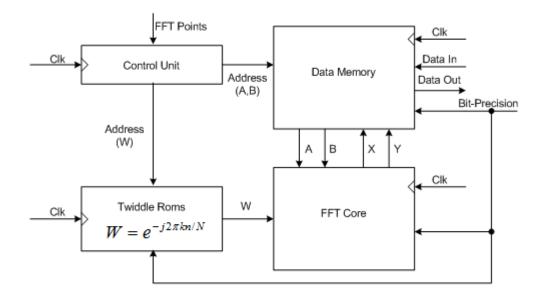

| 6.3.1 FFT Processor Architectures                                                      |     |

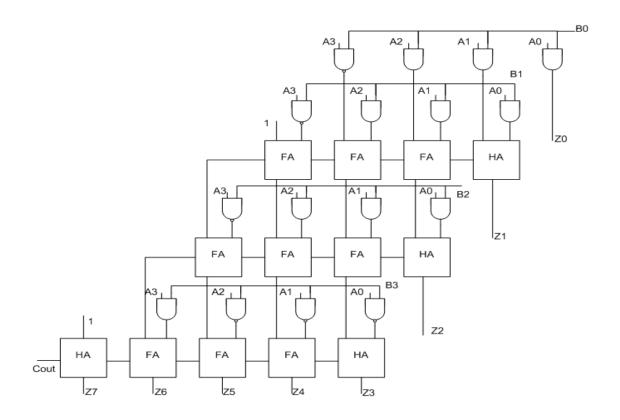

| 6.3.2 Baugh Wooley Multiplier                                                          | 101 |

| 6.4 Conclusion                                            |  |

|-----------------------------------------------------------|--|

| CHAPTER SEVEN:                                            |  |

| 7.1 INTRODUCTION                                          |  |

| 7.2 STANDARD DYNAMIC LOGIC CIRCUITS                       |  |

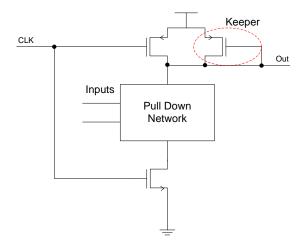

| 7.2.1 General Operation of Dynamic Logic Circuits         |  |

| 7.2.2 Design trade-off in dynamic logic circuit           |  |

| 7.2.3 Variable Threshold Voltage Keeper                   |  |

| 7.2.4 Dynamic body bias generator                         |  |

| 7.2.5 Optimising V <sub>dd2</sub> for Power Delay Product |  |

| 7.3 STATIC RANDOM ACCESS MEMORY                           |  |

| 7.3.1 Memory Cells                                        |  |

| 7.3.2 Sense Amplifier and Pre-charge Circuit              |  |

| 7.3.3 SRAM Leakage Current Reduction Techniques           |  |

| 7.3.3.1 Multi-Threshold CMOS                              |  |

| 7.3.3.2 Variable-Threshold CMOS                           |  |

| 7.4 Conclusion                                            |  |

| CHAPTER EIGHT:                                            |  |

| 8.1 INTRODUCTION                                          |  |

| 8.2 Design Flow                                           |  |

| 8.3 Overall Results                                       |  |

| 8.4 Conclusion                                            |  |

| CHAPTER NINE:                                             |  |

| 9.1 SUMMARY OF RESEARCH CONTRIBUTION                      |  |

| 9.2 FUTURE RESEARCH DIRECTIONS                            |  |

| BIBLIOGRAPHY                                              |  |

| APPENDIX A: IMPLEMENTED ENCOUNTER SCRIPT                  |  |

| APPENDIX B: BUCK CONVERTER PLOT MATLAB CODE               |  |

## **Declaration of Originality**

"I, David Fitrio, declare that the PhD thesis entitled "Power Management Schemes for Ultra Low Power Biomedical Devices" is no more than 100,000 words in length, exclusive of tables, figures, appendices, references and footnotes. This thesis contains no material that has been submitted previously, in whole or in part, for the award of any other academic degree or diploma. Except where otherwise indicated, this thesis is my own work".

Signature

Date

David Fitrio

### Acknowledgement

It has been an honour and a privilege to study at Victoria University. There are many people to thank: Those for the inspiration, those who provided guidance and those whose friendship made difficult times into pleasure. Most of the people listed below have provided inspiration, guidance and friendship.

Before anything else, I must thank God, without Him I won't be the person I am today.

I thank my parents, Mr. Yunus Laisana and Mrs. Helena S. Gotama and my little sister, Davina Stephanie, and her husband, for giving me unconditional love, guidance and support. Their prayers and advice are always be with me. I thank my wife and my sons, Darrell Kenichi Lay (5), and Jason Kenneth Lay (1). Even though we are apart (3245 miles to be exact), but I have their never ending support. Therefore, my thoughts are always with them.

I would like to express my deepest appreciation to my primary supervisor, Associate Professor Aleksandar Stojcevski as whom I have known since our undergraduate days together. His technical guidance, endless discussions, motivations and advice have always been there to help me. Regardless, for research, work or life related, he and his family always gave the best support for me.

I would like to thank my secondary supervisor, Professor Gregory Baxter for his dedication and time for my research. His skills as a researcher combined with his experience in management and hard working ethics have been an example to all of research students under his guidance.

To my colleagues Dr. Ronny Veljanovski, Anand Mohan, Jaideep Chandran, Nikhil Joglekar, Eder Kikianty, Marko Mojic, Rad Zubovic I thank you all. Our relationships have made them my extended family. I remember our regular gym, coffee breaks and "protocol" visits. Since the increase of petrol price from a year ago, my everyday long journey home together with Anand, a fund raiser for our regular treats, has been entertaining.

My gratitude also goes to Victoria University staff member, Professor Ian Rouse, Professor Mike Faulkner, Maria Pylnyk, Shukonya Benka Hayrettin Arisoy, Abdurrahman Kuzucu, Ashley Rouse and more, for their continuous support and help. Especially to our System Administrator, Abdul Hadbah, without his support none of the Micro-tools is up and running.

I would also like to thank Professor Jugdutt (Jack) Singh from LaTrobe University for the advice and support.

Last but not least, to all my friends and flatmates, whom i have shared my life with in the pass five years. 太田総子, who understands me with 愛 and 調理。本当に有難う ございます。

## **List of Figures**

Note to the reader: Many of the design and simulation packages used in this thesis do not permit the use of super-scripts and sub-scripts in the production of the figures. As a result many symbols appear in a standard format.

| Figure 1.1: Examples of Biomedical enhancements through CMOS technology                                                                                                                                                                | 3 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 2.1: Home healthcare system showing a personal network attached to a patient body, together with its supporting system and connection to a health service provider                                                              | 2 |

| Figure 3.1: Energy and Propagation Delay Trade-off for a 0.13 μm CMOS, the energy dissipated is shown as a dashed line, whilst the delay is shown by the solid line                                                                    | 1 |

| Figure 3.2: Illustration of Multiple Supply Voltage Scaling. Two supply voltages are provided being $V_{ddH}$ (high) and $V_{ddL}$ (low). The optimised critical path of the circuit is shown by the red dashed line                   | 2 |

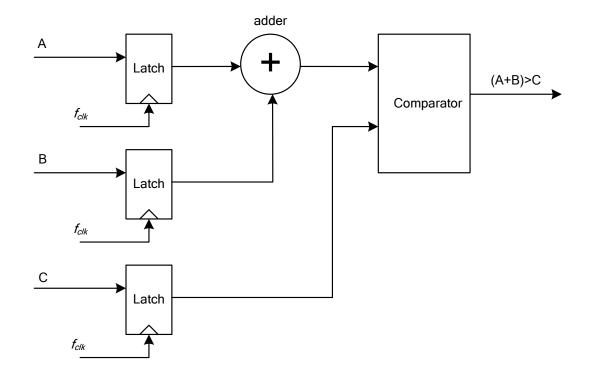

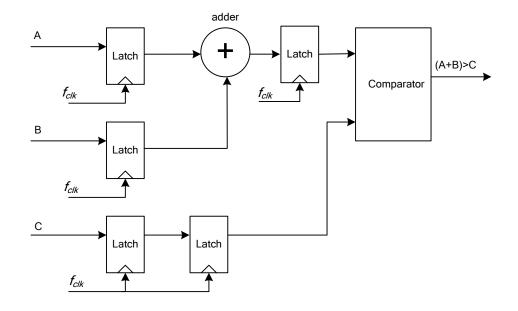

| Figure 3.3: A Simple Datapath Block Diagram                                                                                                                                                                                            | 3 |

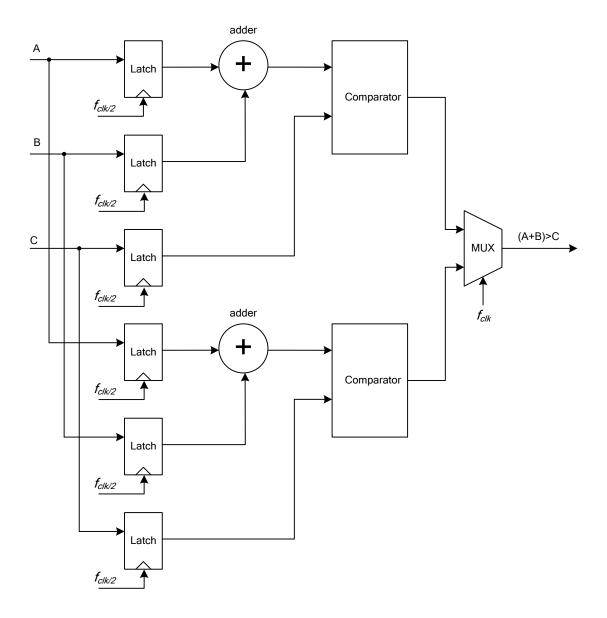

| Figure 3.4: Parallel Architecture Implementation of the Datapath                                                                                                                                                                       | 4 |

| Figure 3.5: Pipelined Architecture Implementation of the datapath                                                                                                                                                                      | 5 |

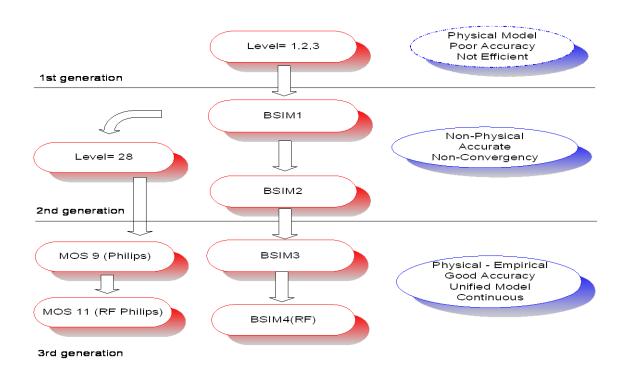

| Figure 3.6: Evolution of MOS transistor models                                                                                                                                                                                         | 7 |

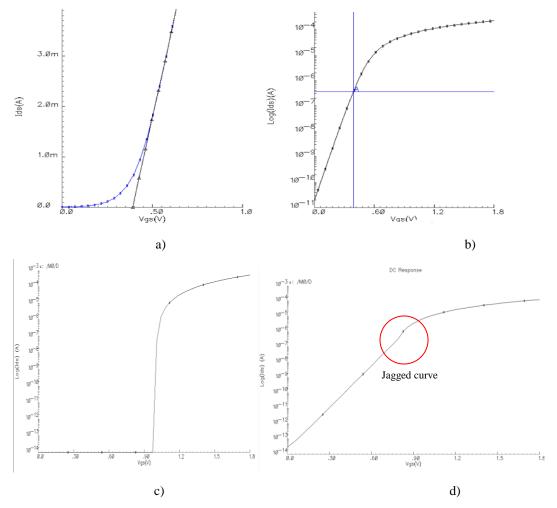

| <ul> <li>Figure 3.7: a) Threshold Voltage Plot, b) Smooth transitional of Log (<i>I</i><sub>ds</sub>) current for BSIM3, c) Subthreshold leakage current unavailability for Level-1 MOS, d) Rough transitions in Level-3 MOS</li></ul> | 8 |

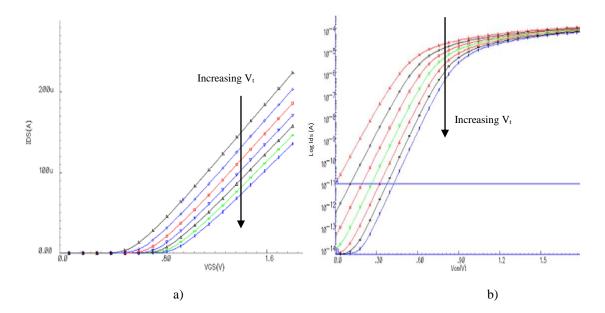

| Figure 3.8: a) Effects of substrate voltage variation on threshold voltage ( $V_t$ ), b)<br>Log ( $I_{ds}$ ), leakage current plot of Figure a)                                                                                        | 9 |

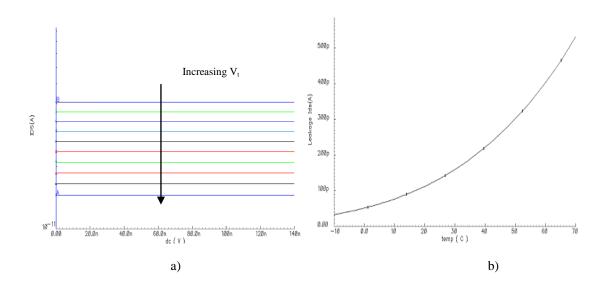

| Figure 3.9: a) $I_{ds}$ current in cut-off region from Figure 3.8 a) enlarged in view, b)<br>$I_{ds}$ Leakage versus Temperature                                                                                                       | 0 |

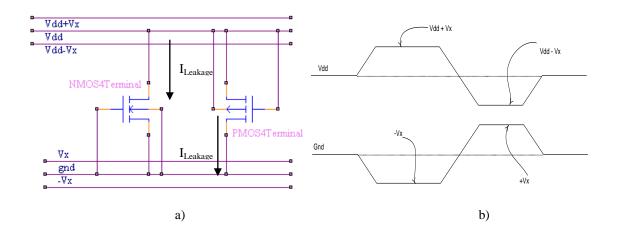

| Figure 3.10: a) MOS under normal biasing scheme, b) Voltage control level of the biasing scheme                                                                                                                                        | 1 |

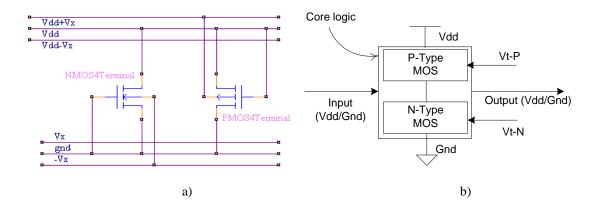

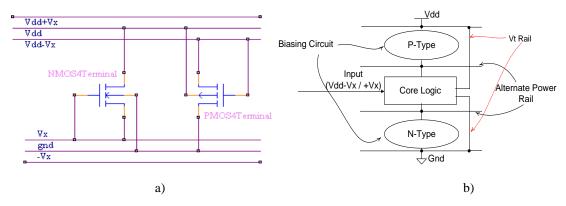

| Figure 3.11: a) MOS under $V_s$ reverse biasing scheme, b) Circuit implementation 32                                                                                                                                                   | 2 |

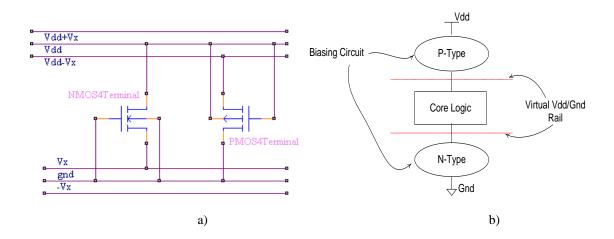

| Figure 3.12: a) MOS under gate voltage reverse biasing scheme, b) Circuit implementation                                                             | . 33 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.13: a) MOS under substrate biasing scheme, b) Circuit implementation                                                                        | . 33 |

| Figure 3.14: a) MOS under source-gate voltage offset biasing scheme, b) Circuit Implementation.                                                      | . 34 |

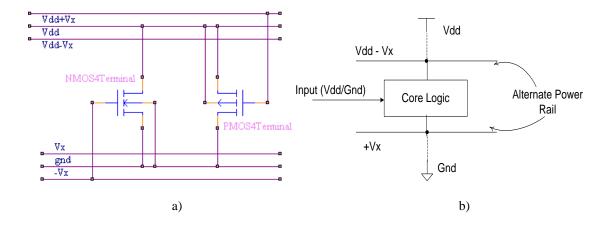

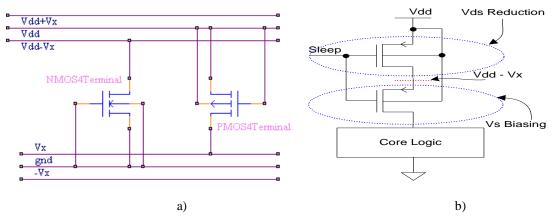

| Figure 3.15: a) MOS under $V_{ds}$ reduction scheme, b) Stacking Effect                                                                              | . 34 |

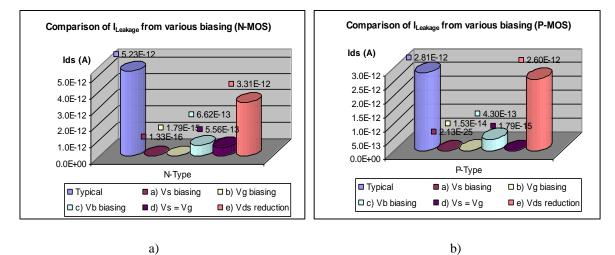

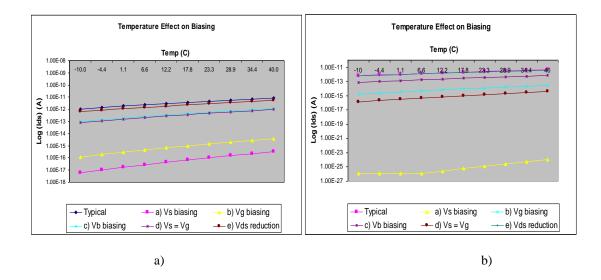

| Figure 3.16: Comparisons of the simulated leakage current result of a) N-type, b)<br>P-type MOS under different biasing scheme                       | . 35 |

| Figure 3.17: a) N-MOS, b) P-MOS biasing techniques against temperature for the various biasing schemes as described in the text.                     | . 36 |

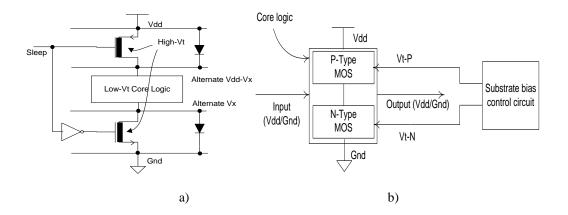

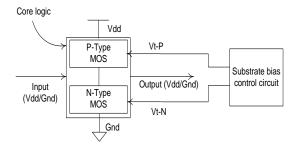

| Figure 3.18 a) MTCMOS circuit architecture, b) VTCMOS circuit architecture                                                                           | . 37 |

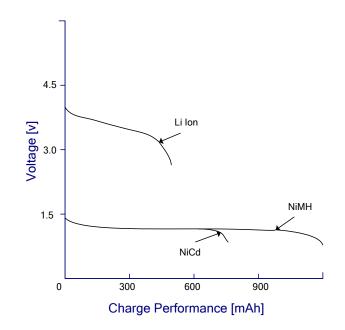

| Figure 4.1: Typical discharge characteristics for AA-type Nickel Cadmium (NiCd),<br>Nickel Metal Hydride (NiMH), and Lithium Ion (Li-Ion) cells [55] | . 41 |

| Figure 4.2: Three different loads applied to the battery model, (a) constant current, (b) resistive load, (c) power load.                            | . 44 |

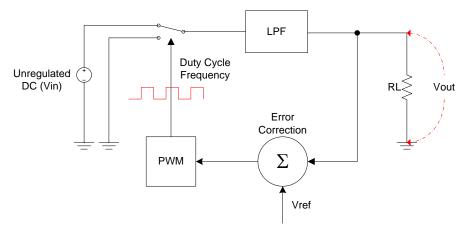

| Figure 4.3: DC-DC converters driven by a PWM switching circuit                                                                                       | . 48 |

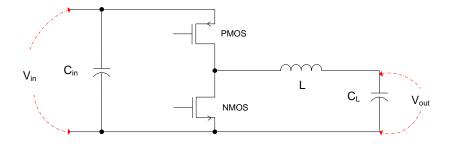

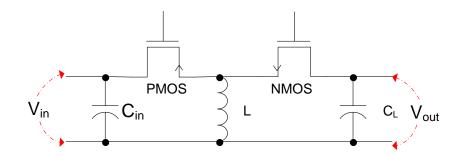

| Figure 4.4: CMOS Buck converter circuit diagram                                                                                                      | . 49 |

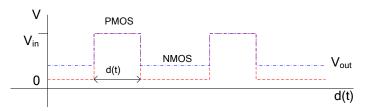

| Figure 4.5: Power Transistors Periodic Output Voltage Waveform of the buck converter.                                                                | . 50 |

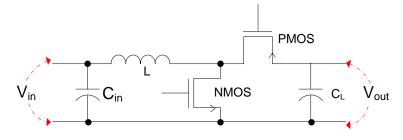

| Figure 4.6: CMOS Boost Converter Circuit diagram.                                                                                                    | . 50 |

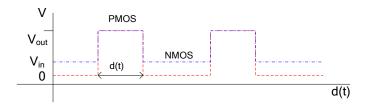

| Figure 4.7: Periodic output voltage steady state diagram of a boost converter                                                                        | . 51 |

| Figure 4.8: Buck-Boost Converter Circuit Diagram                                                                                                     | . 52 |

| Figure 4.9: Periodical Steady-State Waveform of a Buck-Boost Converter.                                                                              | . 52 |

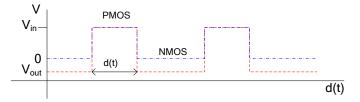

| Figure 5.1: "Just enough" operation in dynamic $V_{dd}$ scaling                                                                                      | . 55 |

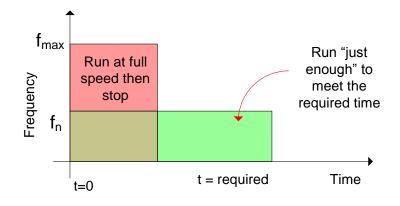

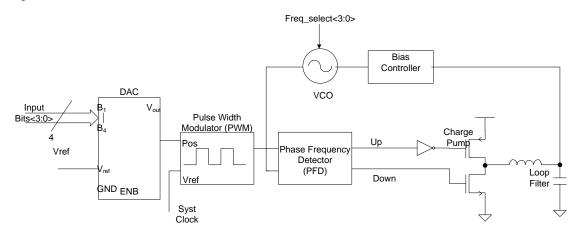

| Figure 5.2: DVS Implementation System Architecture                                                                                                   | . 57 |

| Figure 5.3: 4 bits R-2R Voltage Mode Resistor Ladder DAC                                                                                             | .61  |

| Figure 5.4: 4 bits R-2R Current Mode Resistor Ladder DAC.                                                                                            | .61  |

| Figure 5.5: 4 bits R-2R Wide Swing Current Mode Resistor Ladder DAC.                                                                                 | . 63 |

| Figure 5.6: Current Splitting Principle in NMOS DAC, with reference current $(I_{REF})$ flow through in each W-2W transistor branch with intercorrelation mismatch correction transistor shown in the dashed box                                       | 64 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

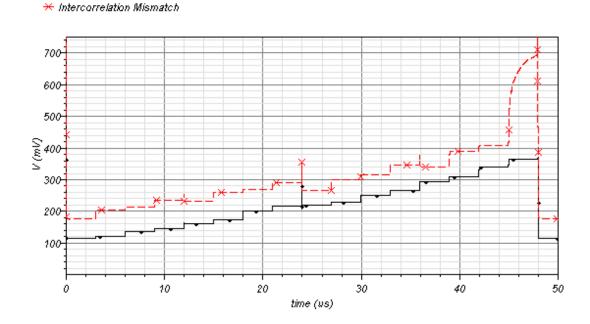

| Figure 5.7: Simulation Results of the effect of Intercorrelation Mismatch in transistor-only DAC with the application of the correction transistor. The linearity of the DAC is improved by using the correction transistor as shown by line in black. | 65 |

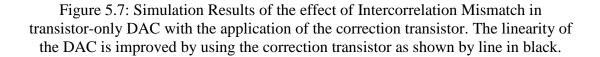

| Figure 5.8: The Comparison of four different Voltage Biases (100%, 90%, 70% and 50%) on transistor only DAC, which directly effect the DAC linearity                                                                                                   | 66 |

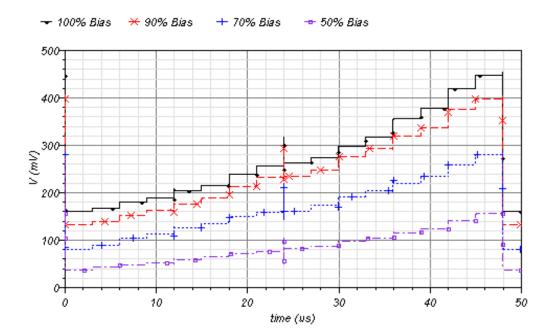

| Figure 5.9: The MOS Current Steered DAC with the process insensitive bias voltage shown in the dashed box.                                                                                                                                             | 67 |

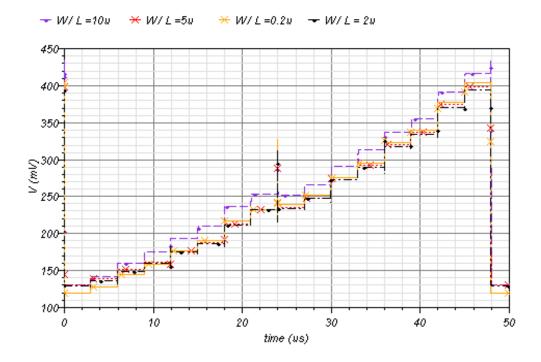

| Figure 5.10: The comparison of different transistor size on linearity in the MOS only transistor DAC. Four different transistor width were simulated; 10 $\mu$ m, 5 $\mu$ m, 2 $\mu$ m and 0.2 $\mu$ m                                                 | 68 |

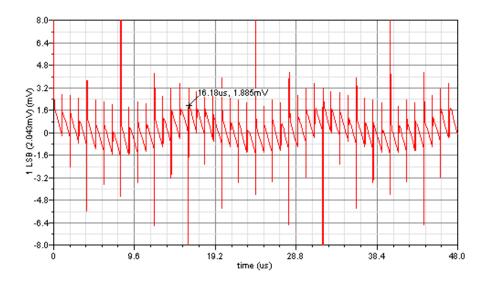

| Figure 5.11: An INL @ 150 MHz plot of the MOS only transistor DAC                                                                                                                                                                                      | 69 |

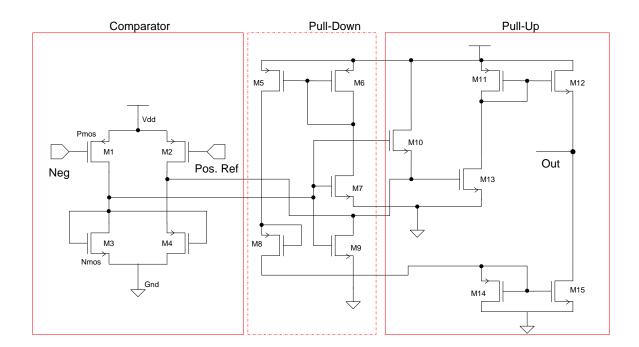

| Figure 5.12: Two Stage Comparator Functioning as Pulse Width Modulator, with the pull-down and pull-up circuit for faster output response                                                                                                              | 70 |

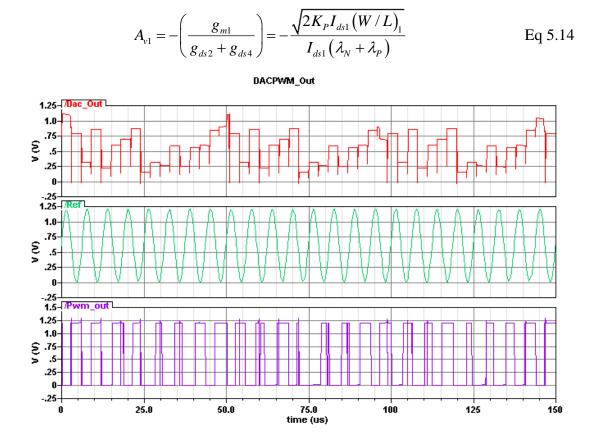

| Figure 5.13: Pulse Width Modulator Circuit Output Waveforms (Pwm_OUT),<br>which compares the DAC circuit output (Dac_Out) to the reference clock<br>signal (Ref)                                                                                       | 72 |

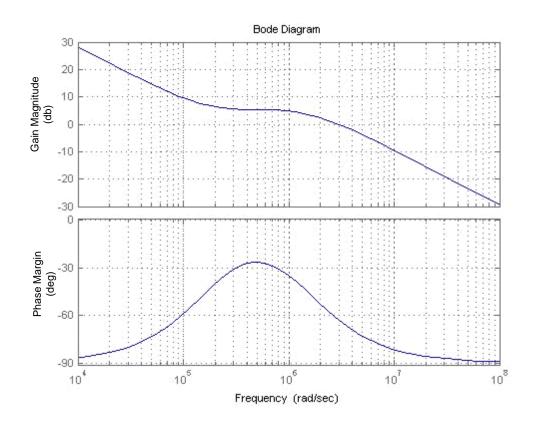

| Figure 5.14 Pulse Width Modulator Circuit Gain Magnitude (db) and Phase Margin (deg) Bode Diagram                                                                                                                                                      | 73 |

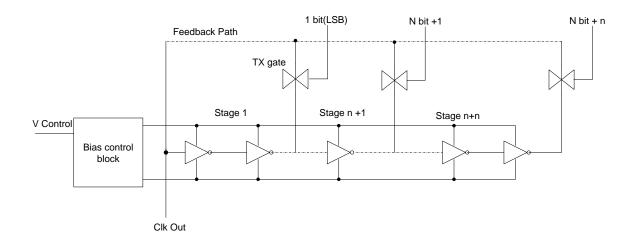

| Figure 5.15: The designed ring oscillator partitioned with transmission gates to allow frequency selection and bias control for frequency fine tuning                                                                                                  | 74 |

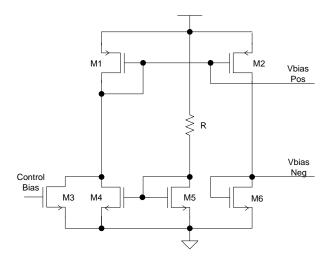

| Figure 5.16: Bias Control Block of the ring oscillator which generates positive and negative voltage bias to the inverter stages                                                                                                                       | 75 |

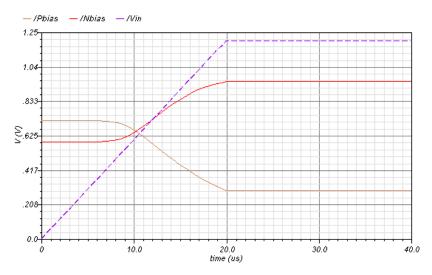

| Figure 5.17: The output magnitude of $V_{bias}$ -Pos (Pbias) and $V_{bias}$ -Neg (Nbias) of the control bias with input control bias voltage (Vin).                                                                                                    | 75 |

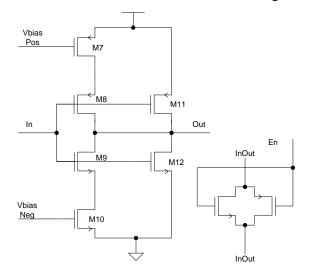

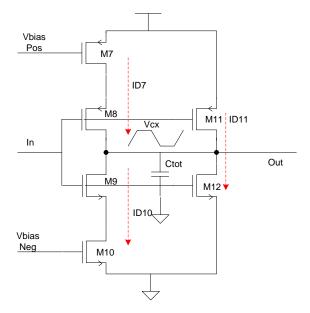

| Figure 5.18: Current-Starved VCO Inverter and Transmission Stage Schematic                                                                                                                                                                             | 76 |

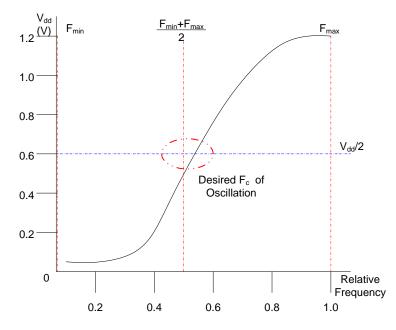

| Figure 5.19: Desired oscillator circuit centre frequency performance as compared to the ideal centre frequency from the average of $F_{min}$ and $F_{max}$                                                                                             | 77 |

| Figure 5.20: The two current paths of the oscillator inverter stage. The current starve paths of ID7 and ID10 and the driving current path of ID11                                                                                                     | 78 |

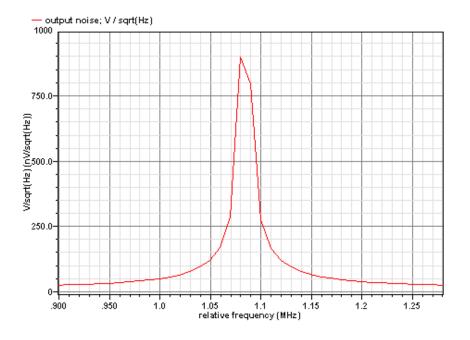

| Figure 5.21: VCOs Centre Frequency Response.                                                                                                                                                                                                           | 80 |

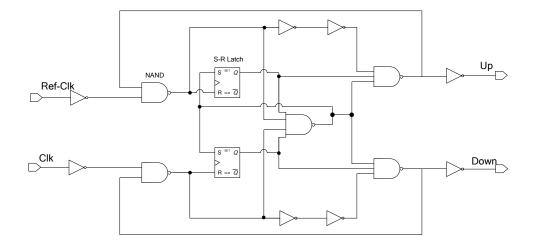

| Figure 5.22: Phase and Frequency Detector (PFD) comprises of 5 Nand gates, 8 inverters and 2 latches                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

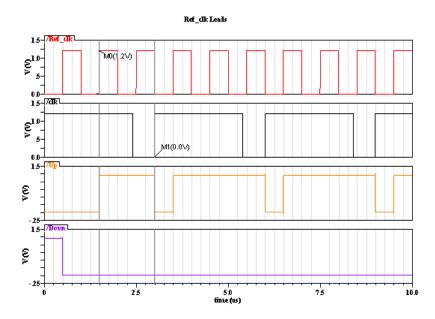

| Figure 5.23: The Up signal is generated if the Clk signal lags the Ref_Clk signals.<br>The waveforms shows Ref-Clk signal in the first panel, Clk signal on the<br>second panel, output Up on the third panel and output Down on the last or<br>bottom panel                                                                                                                          |

| Figure 5.24: The PFD generates Down signals if Clk signal leads the Ref_Clk signal                                                                                                                                                                                                                                                                                                    |

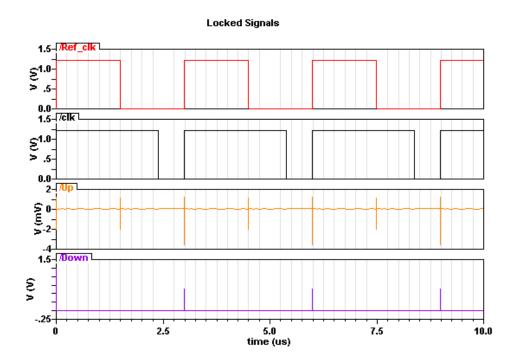

| Figure 5.25: The Locked Condition happens when the Clk signal is equal to the Ref_Clk signal                                                                                                                                                                                                                                                                                          |

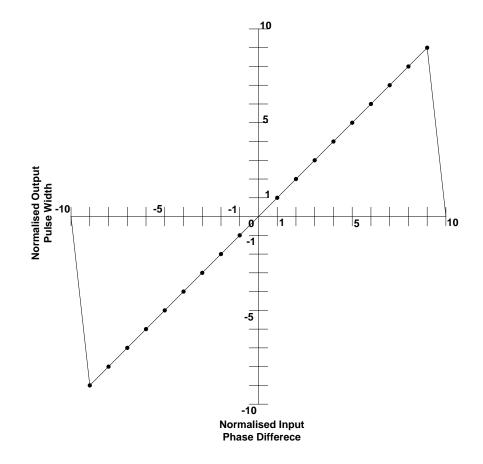

| Figure 5.26: The Zero zone transfer characteristics of the PFD from a SpectreS simulation®                                                                                                                                                                                                                                                                                            |

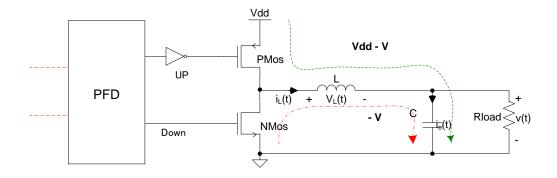

| Figure 5.27 The Buck Converter in a DVS system, shown connected to the output of the PFD block. The charging current path ( $V_{dd}$ - $V$ ) is shown by the green arrow, while the discharging current path (- $V$ ) is shown by the red arrow                                                                                                                                       |

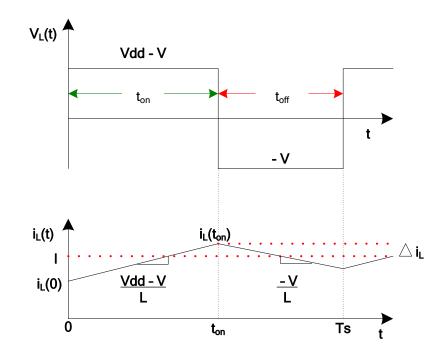

| Figure 5.28: Voltage-Current Response of On and Off Pulse Time across the inductor. The inductor voltage $(V_L)$ is shown in the top graph and the inductor current $(I_L)$ is shown in the bottom graph                                                                                                                                                                              |

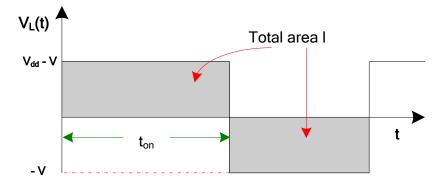

| Figure 5.29: Overall On and Off Pulse Area                                                                                                                                                                                                                                                                                                                                            |

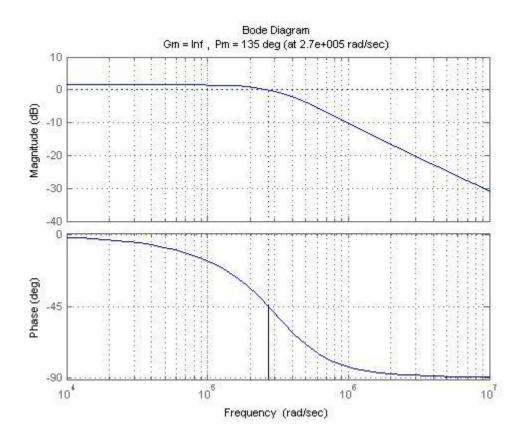

| Figure 5.30: Gain Magnitude and Phase Margin Bode Diagram of the Designed<br>Buck Converter                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                       |

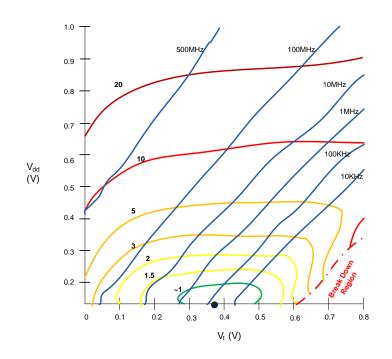

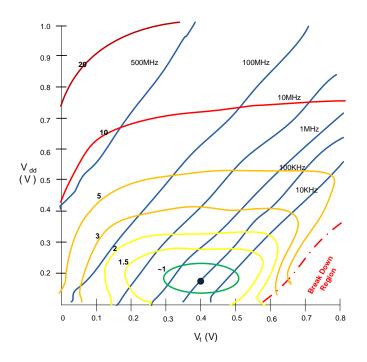

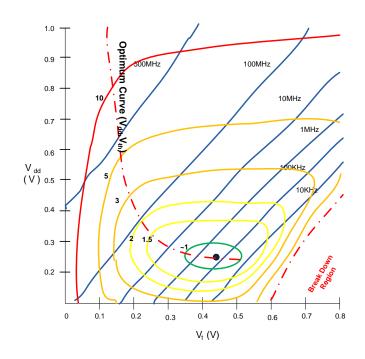

| Figure 6.1: Energy-Performance Profile of the Ring Oscillator Circuit with activity factor of one ( $\alpha = 1$ ). The stable operating frequencies are indicated by the straight lines and the curves represent the normalised energy dissipated by the oscillator. The red dot represents the optimum operating point of the circuit 96                                            |

| factor of one ( $\alpha = 1$ ). The stable operating frequencies are indicated by the straight lines and the curves represent the normalised energy dissipated by the                                                                                                                                                                                                                 |

| <ul> <li>factor of one (α = 1). The stable operating frequencies are indicated by the straight lines and the curves represent the normalised energy dissipated by the oscillator. The red dot represents the optimum operating point of the circuit 96</li> <li>Figure 6.2: Energy-Performance Profile of the Ring Oscillator Circuit with half</li> </ul>                            |

| <ul> <li>factor of one (α = 1). The stable operating frequencies are indicated by the straight lines and the curves represent the normalised energy dissipated by the oscillator. The red dot represents the optimum operating point of the circuit 96</li> <li>Figure 6.2: Energy-Performance Profile of the Ring Oscillator Circuit with half activity factor (α = 0.5)</li></ul>   |

| factor of one ( $\alpha = 1$ ). The stable operating frequencies are indicated by the straight lines and the curves represent the normalised energy dissipated by the oscillator. The red dot represents the optimum operating point of the circuit 96<br>Figure 6.2: Energy-Performance Profile of the Ring Oscillator Circuit with half activity factor ( $\alpha = 0.5$ )          |

| factor of one ( $\alpha = 1$ ). The stable operating frequencies are indicated by the<br>straight lines and the curves represent the normalised energy dissipated by the<br>oscillator. The red dot represents the optimum operating point of the circuit 96<br>Figure 6.2: Energy-Performance Profile of the Ring Oscillator Circuit with half<br>activity factor ( $\alpha = 0.5$ ) |

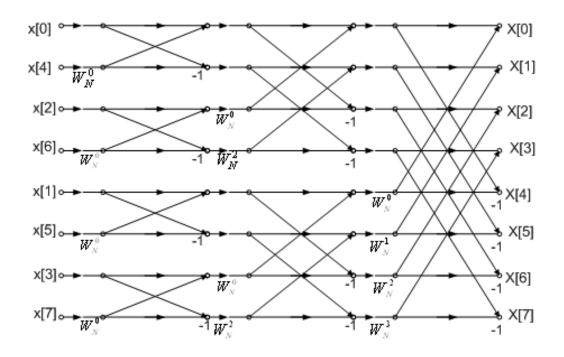

| Figure 6.8: Gate level implementation of 4x4 bit Baugh Wooley Multiplier Gates<br>Representation                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.1: A Typical dynamic logic configuration with a keeper circuit                                                                                                                                                                                                                                                                                                                               |

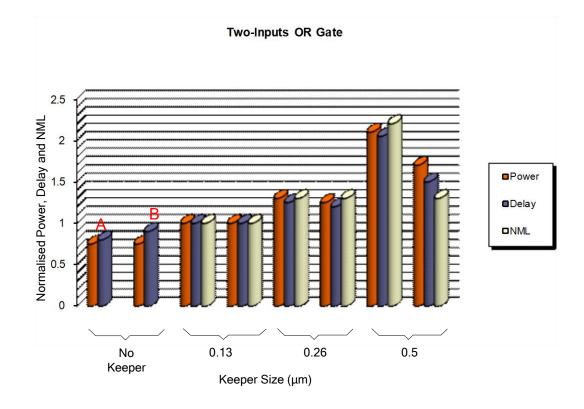

| Figure 7.2: Simulation of the effects on power, delay and NML characteristics of a two input OR gate by increasing keeper transistor size of the circuit. Group A: only one input is excited and the other grounded, Group B: all inputs are excited with the same signal                                                                                                                             |

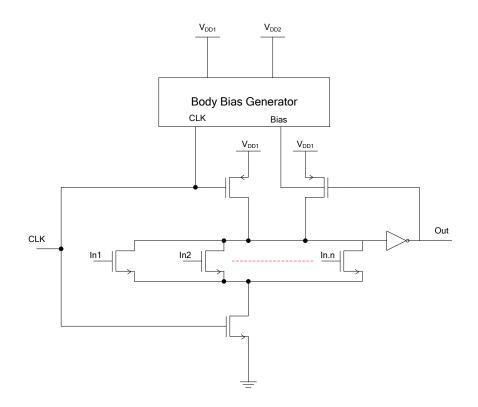

| Figure 7.3: An N input dynamic OR logic together with a Body Bias Generator and variable threshold keeper                                                                                                                                                                                                                                                                                             |

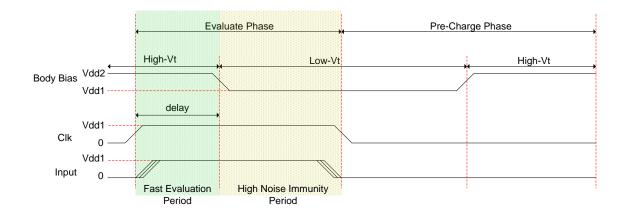

| Figure 7.4: Operational waveform sequence of the variable threshold voltage keeper technique. The evaluation and pre-charge phase is separated by the red dashed lines. The High- $V_t$ is shaded in green and Low- $V_t$ in red to differentiate the body bias condition to the keeper                                                                                                               |

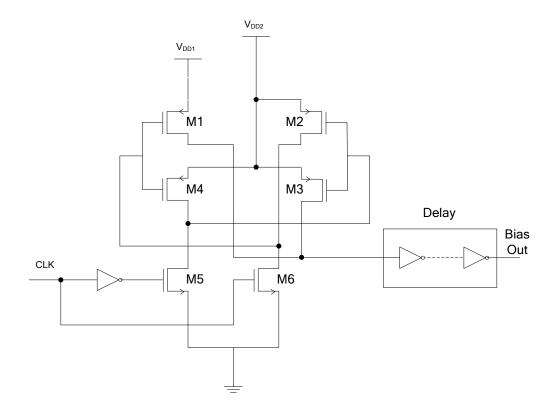

| Figure 7.5: Body Bias Generator circuit with the non-inverting worst case delay shown in the box                                                                                                                                                                                                                                                                                                      |

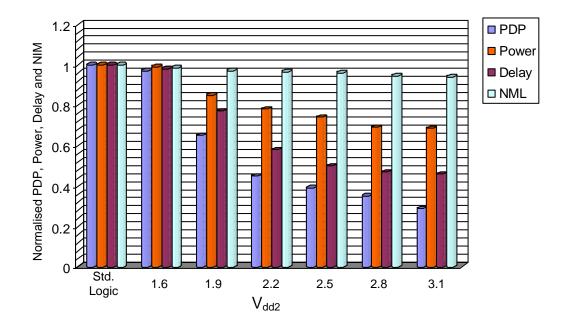

| Figure 7.6: The effect of different $V_{dd2}$ amplitude on PDP, power, delay and NML characterisation for the variable threshold keeper technique                                                                                                                                                                                                                                                     |

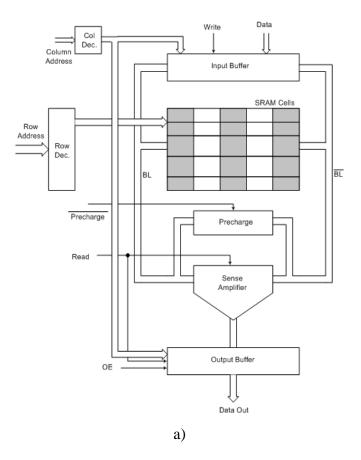

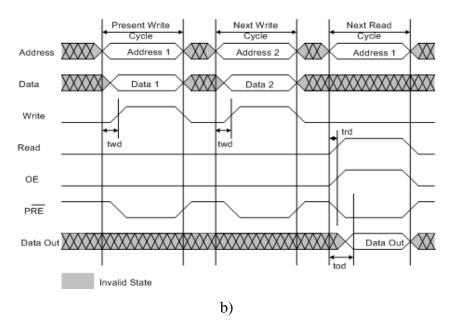

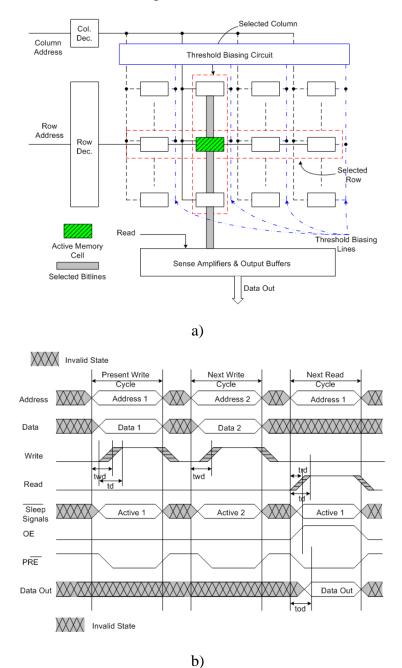

| Figure 7.7: a) Conventional SRAM topology which consists of an input buffers,<br>pre-charge and amplifier circuits, output buffers and bit addressing decoder b)<br>Read and Write cycles of SRAM. The waveforms depict the appropriate<br>control signal level                                                                                                                                       |

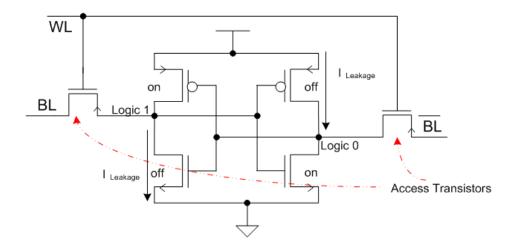

| Figure 7.8: 1-Bit of SRAM memory cell circuit with access transistors bit lines (BL) and write line access                                                                                                                                                                                                                                                                                            |

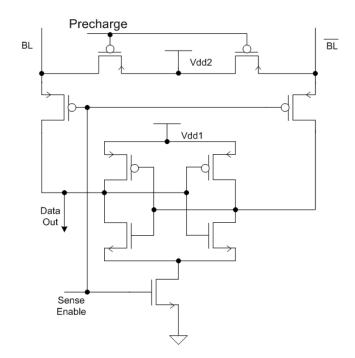

| Figure 7.9: The CMOS inverter latch topology in the conventional sense amplifier circuit                                                                                                                                                                                                                                                                                                              |

| Figure 7.10: MTCMOS circuit architecture principal                                                                                                                                                                                                                                                                                                                                                    |

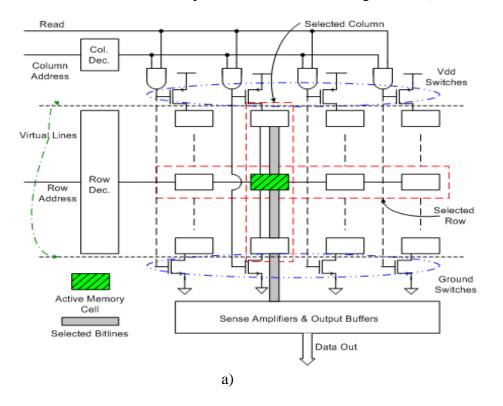

| Figure 7.11: MTCMOS a) Memory cells array structure with the active cell shaded<br>in green. The structure consists of switches to reduce the current in the in-<br>active cells, b) Operation signals in read and write cycles with additional set-<br>up time for the active cell to avoid data error due to a different voltage level<br>during the transition from an active to a non-active cell |

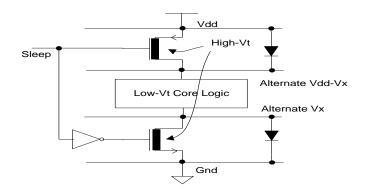

| Figure 7.12: VTCMOS circuit architecture                                                                                                                                                                                                                                                                                                                                                              |

| Figure 7.13: VTCMOS. a) Memory cells array structure with the active cell shaded<br>in green. The structure consists of threshold bias generator block. , b)<br>Operation signals in read and write cycles with additional set-up time for the                                                                                                                                                        |

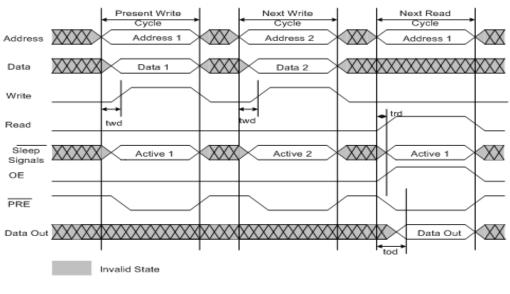

| active cell to avoid data error due to a different threshold voltage level during the transition from an active to a non-active cell                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

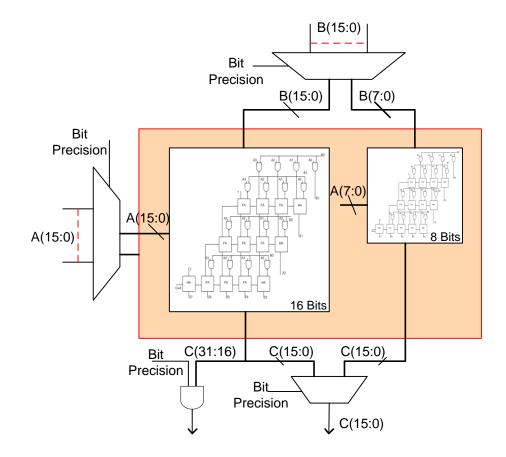

| Figure 8.1: 8 bit and 16 bit scalable Baugh Wooley multiplier core with the input addressing Mux and scalable bit precision output to select different output bits, C, size. Both input A and B are processed according to the bit length which enables the appropriate multiplier bit                                                                                                                                                                                                                                     |

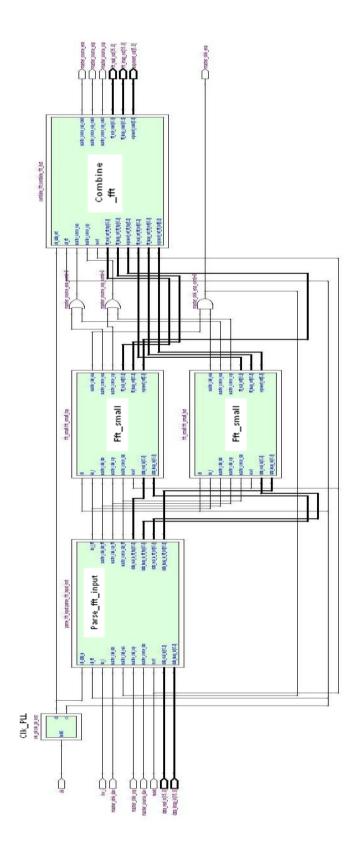

| Figure 8.2: Synopsys RTL Synthesis Block View, which consists of the core logic,<br>memory banks for data caching and output latches                                                                                                                                                                                                                                                                                                                                                                                       |

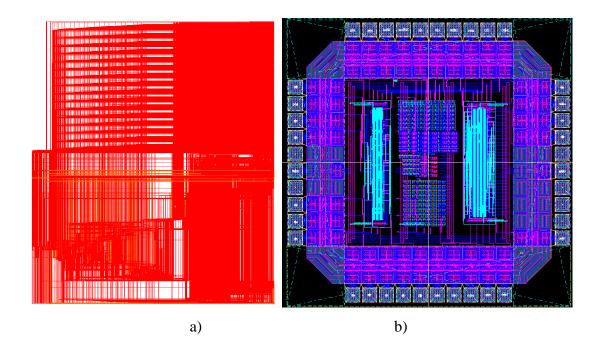

| Figure 8.3: a) Synopsis synthesis RTL View of the FFT design and b) Cadence gates Layout of the FFT cells together with the pads                                                                                                                                                                                                                                                                                                                                                                                           |

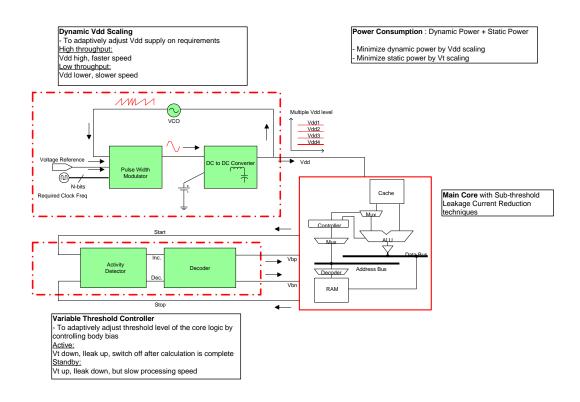

| Figure 8.4: Overall Integration blocks, which consists of the dynamic power reduction block and the static power reduction. Both of the power reduction techniques were applied to a FFT main processor core                                                                                                                                                                                                                                                                                                               |

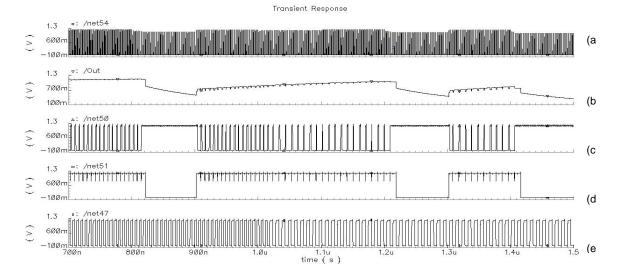

| Figure 8.5: $V_{dd}$ Scaling with Frequency Variation Post-Layout Simulation Result.<br>Shown in the panel a) is the reference frequency from the oscillator circuit.<br>Panel e) describes the series of pulse modulated output waveforms. Both of<br>the signals, a) and e), are passed through into the Phase and Frequency<br>Detector which generates Up, shown in d) and Down, shown in c) signals.<br>The output waveform b), is the locked voltage which is used by the FFT<br>processor as power supply, $V_{dd}$ |

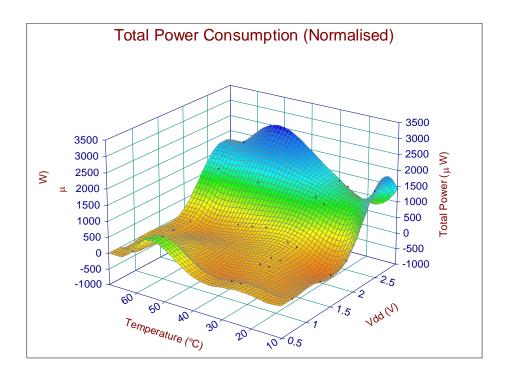

| Figure 8.6: Total power consumption versus $V_{dd}$ and Temperature of the Post-<br>Layout System. The system minimum power consumption is optimised at<br>between 1 to 2.25 Volts $V_{dd}$ , as it lies at the lowest power bed scale. There is a<br>power spike shown at 55 degree Celsius together with 3 Volts of operation<br>which is caused by the device breakdown                                                                                                                                                 |

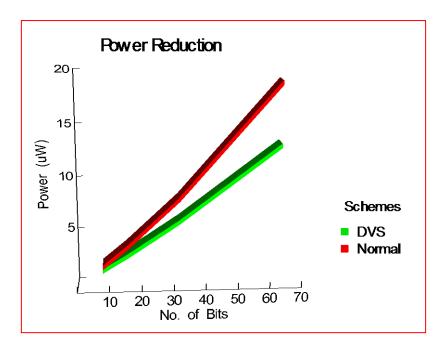

| Figure 8.7: The Simulated power comparison plot of normal and DVS scheme,<br>shown in green line, and on the FFT multiplier core, shown in red line                                                                                                                                                                                                                                                                                                                                                                        |

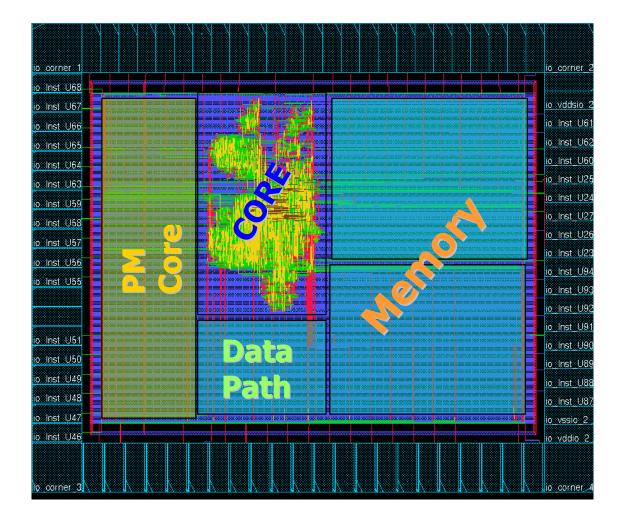

| Figure 8.8: Power Management and FFT Core Design Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# **List of Tables**

| Table.1.1: Performance characteristics of commonly used batteries          | . 15 |

|----------------------------------------------------------------------------|------|

| Table 4.1: Comparison of system run-time                                   | . 47 |

| Table 8.1: Post-Layout simulation result summary of the modeled DVS System | 133  |

| Table 8.2: Power Performance of DVS System in the implemented FFT Core     | 134  |

## **List of Abbreviations**

| AC   | Alternating Current                     |

|------|-----------------------------------------|

| ADC  | Analog to Digital Converter             |

| ADSL | Asymmetric Digital Subscriber Line      |

| ALU  | Arithmetic Logic Unit                   |

| ASIC | Application Specific Integrated Circuit |

| BAN  | Body Area Network                       |

| BL   | Bit Lines                               |

| BSIM | Berkeley Short-Channel IGFET Model      |

| CMOS | Complementary Metal Oxide Semiconductor |

| CPU  | Central Processing Unit                 |

| CV   | Capacitance-Voltage                     |

| DAC  | Digital to Analog Converter             |

| DC   | Direct Current                          |

| DFT  | Discrete Fourier Transform              |

| DIF  | Decimation in Frequency                 |

| DIT  | Decimation in Time                      |

| DNL  | Differential Non-Linearity              |

| DR   | Dynamic Range                           |

| DRAM | Dynamic Random Access Memory            |

| DSP  | Digital Signal Processor                |

| DVS  | Dynamic Voltage Scaling                 |

| DVFS | Dynamic Voltage and Frequency Scaling   |

| EDA  | Electronic Design Automation            |

| EDP  | Energy Delay Product                    |

| ESR  | Equivalent Series Resistance            |

| FET  | Field Effect Transistor                 |

|      |                                         |

| FFT    | Fast Fourier Transform                                  |

|--------|---------------------------------------------------------|

| FPGA   | Field Programmable Gate Array                           |

| FSM    | Finite State Machine                                    |

| IC     | Integrated Circuit                                      |

| ICT    | Information and Communication Technology                |

| INL    | Integral Non-Linearity                                  |

| IV     | Current-Voltage                                         |

| ISDN   | Integrated Services Digital Network                     |

| LCM    | Leakage Current Monitor                                 |

| Li-Ion | Lithium Ion                                             |

| LLUL   | Low Leakage, Ultra Low Leakage                          |

| LPF    | Low Pass Filter                                         |

| LSB    | Least Significant Bit                                   |

| MEMS   | Micro-Electro-Mechanical Systems                        |

| MOS    | Metal-Oxide-Semiconductor                               |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor       |

| MSB    | Most Significant Bit                                    |

| MTCMOS | Multi-Threshold Complementary Metal Oxide Semiconductor |

| MUX    | Multiplexers                                            |

| NMOS   | Negative-Channel Metal Oxide Semiconductor              |

| NiCD   | Nickel-Cadmium                                          |

| NiMH   | Nickel-Metal Hydride                                    |

| NML    | Noise Margin                                            |

| PAN    | Personal Area Network                                   |

| PDP    | Power Delay Product                                     |

| PFD    | Phase Frequency Detector                                |

| PFM    | Pulse Frequency Modulation                              |

| PLL    | Phase Locked Loop                                       |

| PMOS   | Positive-Channel Metal Oxide Semiconductor              |

| PWM    | Pulse Width Modulation                                  |

| R-2R   | Resistor to Two Resistor Weighted Network               |

|        |                                                         |

| RDD    | Responsive Drug Delivery                                   |  |  |

|--------|------------------------------------------------------------|--|--|

| RAM    | Random Access Memory                                       |  |  |

| RF     | Radio Frequency                                            |  |  |

| RTL    | Register Transfer Logic                                    |  |  |

| SOC    | System on Chip                                             |  |  |

| SR     | Slew Ratio                                                 |  |  |

| SRAM   | Static Random Access Memory                                |  |  |

| VCO    | Voltage Controlled Oscillator                              |  |  |

| VLSI   | Very Large Scale Integration                               |  |  |

| VTC    | Voltage Transfer Characteristics                           |  |  |

| VTCMOS | Variable Threshold Complementary Metal Oxide Semiconductor |  |  |

| W-2W   | Width to two Width Transistor Ratio                        |  |  |

| WBAN   | Wide Body Area Network                                     |  |  |

| WL     | Width and Length                                           |  |  |

## **List of Publications**

- D.Fitrio, J.Singh, A.Stojcevski, "Dynamic Voltage Scaling for Power Aware Fast Fourier (FFT) Transform," *Lecture Notes on Computer Science*, Springer-Verlag ACSAC, pp. 52-64, 2005.

- 2. D.Fitrio, A.Stojcevski, J.Singh, "Leakage Current Reduction Techniques for Subthreshold Circuit in a Simulation Environment," Published in *Best of Book, AMSE Journal Press*, 2004.

- D.Fitrio, A.Stojcevski, J.Singh, "Ultra Low Power Weak Inversion Current Steered Ditital to Analog Converter," 2006 IEEE Asia Pacific Conference on Circuits and Systems. Ed(s). Y P Yang. IEEE, pp.1545-1548, 2006.

- D.Fitrio, J.Singh, A.Stojcevski, "Energy Efficient Low Power Shared-Memory Fast Fourier Transform (FFT) Processor with Dynamic Voltage Scaling," SPIE International Symposium on Microelectronics: Design, Technology and Packaging II, Vol. 6035, pp.69-79, 2006.

- 5. D.Fitrio, J.Singh, A.Stojcevski, "Dynamic Voltage Scaling Implementation for Power Management," *IFIP WG 10.5 Conference on Very Large Scale Integration-System On a Chip*, pp.459-464, 2005.

- 6. D.Fitrio, J.Singh, A.Stojcevski, "Energy Efficient Shared-Memory Fast Fourier Transform (FFT) Processor," *ATcrc Telecommunications and Networking Conference*, 2005.

- 7. A.Stojcevski, V.Soundararaman, D.Fitrio, A.Zayegh, "Analog to Digital Converter for Dual-Standard Mobile Receiver," *IEEE International Conference on Modelling and Simulation (ICMS)*, 2005.

- 8. A.Stojcevski, K.Y. Law, D.Fitrio, A.Zayegh, "Modelling and Simulation of a Data Conversion Architecture for a Bluetooth Device," *IEEE International Conference on Modelling and Simulation (ICMS)*, 2005.

- 9. D.Fitrio, A. Stojcevski, J. Singh, "Subthreshold Leakage Current Reduction Techniques for Static Random Access Memory," *SPIE International Symposium on Smart Materials, Nano and Micro-Smart Systems*, Vol. 5649. pp. 673-683, 2004.

- D.Fitrio, A. Stojcevski, J. Singh, "Leakage Current Reduction Techniques for Subthreshold Circuit in a Simulation Environment," *International Conference on Modelling and Simulation (ICMS 04).* Ed(s). Y. Municio Y and Angle M Qento. Association for Modelling and Simulation in Enterprise (AMSE), Palemcia, Espana, pp. 61-62, 2004.

- 12. V. Vibhute, D. Fitrio, J. Singh, A. Zayegh, A.Stojcevski, "A Tunable VCO for Multistandard Mobile Receiver," *IEEE International Workshop on Electronic Design Test and Application (DELTA)*, 2003.

- 13. V. Vibhute, D. Fitrio, J. Singh, A. Zayegh, A.Stojcevski, "MEMS components for front end of Direct Conversion Receiver Architecture," *SPIE's International Symposium on Microelectronics, MEMS and Nanotechnology*, Vol. 5276, pp. 515-523, 2003.

### Abstract

Device power dissipation has grown exponentially due to the rapid transistor technology scaling and increased circuit complexity. Motivated by the ultra low power requirements of emerging implantable and wearable biomedical devices, novel power management schemes are presented in this thesis to increase device run-time. The schemes involve several techniques suitable for ultra low power biomedical integrated circuit design.

This thesis presents a combination of two novel power reduction schemes to reduce the total device power comprising of dynamic and static power dissipation. One of the schemes used is the supply voltage ( $V_{dd}$ ) scaling, also known as Dynamic Voltage Scaling (DVS). DVS is an effective scheme to reduce dynamic power ( $P_{dynamic}$ ) dissipation. The DVS architecture primarily consists of a DC-DC power regulator which is customised to handle scaling variability of the  $V_{dd}$ . The implemented DVS can dynamically vary the  $V_{dd}$  from 300 mV to 1.2 V.

The second scheme presented in this thesis to reduce static power ( $P_{static}$ ) dissipation is threshold voltage scaling. The variable threshold keeper technique is used to perform threshold voltage scaling, which comprises of a keeper transistor whose threshold voltage is scaled by a body bias generator. The use of the keeper transistor increases the device noise immunity.

This combination of supply and threshold voltage scaling techniques offers a further reduction in the overall device power dissipation and enhances reliability without degrading circuit speed. A power reduction of 23% to 31% is achievable with up to 90% efficiency. The thesis discusses the primary design challenges of ultra low power biomedical devices. System and circuit levels design techniques are described which help meeting the stringent requirements imposed by the biomedical environment. This thesis presents a new DVS architecture and investigates the effect of lowering the supply voltage combined with threshold voltage scaling on dynamic power dissipation using 0.13 µm ST-Microelectronic® 6-metal layer CMOS dualprocess technology.

## Chapter One: Introduction

#### 1.1 Background of This Research

Australia, as the world's smallest continent, is located in the southern hemisphere of the world. Demographically, Australia comprises of 5% of the world's land area, at 7,692,024 km<sup>2</sup> of world's total 149, 450,000 km<sup>2</sup>, and is the sixth largest country after Russia, Canada, China, USA, and Brazil. However, Australia is 30 times smaller in population when compared with Europe having a population density of just 2.5 people per km<sup>2</sup>. The majority of Australia's population and cities are spread along the coastal areas [1]. As a consequence, primary infrastructure such as medical facilities are located in coastal areas [2]. The infrastructure overlay makes it difficult for people living in rural area to get medical attention.

Although, Australia is known to have adequate medical knowledge and technology, the number of hospitals and medical practitioners are not sufficient to satisfy all patients needs. The Australian government has tried to solve this problem by: increasing the number of hospitals and medical professionals, by making improvements to medical facilities, introduction of flying doctors for rural patients, and increasing research activity in medical fields. However, all of these developments have an impact on medical care cost. Australia needs a cheaper solution to this problem. Therefore, the Australian government have encouraged medical research activity in the field of biomedical engineering [3]. Biomedical Engineering is defined as the application of engineering principles to the field of biology and medical chemistry, as for example in the development of aids or replacements for defective of missing body organs which cause problems to human health. Engineering in this

context is the application of scientific and mathematical principles to the design, manufacturing and operation of the practical devices.

One of the emerging fields in Australian engineering is Microelectronic engineering. Microelectronic engineering, particularly Complementary Metal Oxide Semiconductor (CMOS) integrated circuits, has shown its wide application in many key consumer products from computers, automobiles, consumer electronics and telecommunications equipment. Its wide use in our daily life, has enabled low production and material cost. The Australian government has recognised CMOS technology as the solution for the missing link in the medical field, and is encouraging researchers to investigate CMOS biomedical portable devices [4, 5].

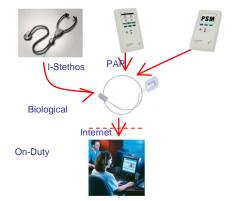

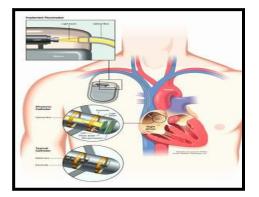

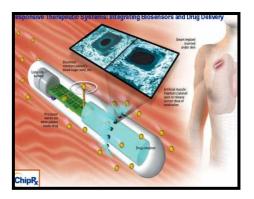

Some of the enhancements in biomedical technology due to CMOS implementation are shown in Figure 1.1. A Home tele-monitoring system as shown in Figure 1.1a; it is a personal home health monitoring system, which is capable of measuring heart rate, pulmonary arterial pressure and breathing regularity [6]. The collected measurements are then packaged and sent via an internet connection to the hospital and further diagnosed by medical professionals. The medical professionals would then directly provide, as appropriate, a prescription from the diagnosis or dispatch a medical team for a critical patient. This medical system would be very beneficial for patients residing in rural areas, and could potentially reduce general medical costs. Implantable medical devices have improved in size, function and comfortableness. Electrical pacemakers have replaced the mechanical pacemaker which was very bulky and introduced an unpleasant experience to recipients, as shown in Figure 1.1b) [7, 8]. Another example, shown in Figure 1.1c), is a Response Drug Delivery (RDD) system [9], which is implanted under the skin and is capable of detecting human's blood chemical inadequacy which then releases appropriate medication. The response drug delivery system, or Smart-drug, has proven to be very efficient for diabetes sufferers where constant medication is required. CMOS technology and Micro-Electro-Mechanical systems (MEMS) have resulted in an implantable CMOS retina sensor for sight impaired patients in Figure 1.1d) [10].

a) Home tele-monitoring

b) Electrical Pacemaker

c) Response drug delivery system

d) Implantable CMOS image sensors

Figure 1.1: Examples of Biomedical enhancements through CMOS technology.

### 1.2 Motivation

The motivation behind this research comes from the interest of the candidate in the area of pervasive computing healthcare technologies and wearable biomedical devices. Most of the applications proposed in these areas consist of a sensor, data collecting and communication infrastructure for data transfer.

A biomedical portable device primarily functions as a personal aid device. As the name 'portable' indicates, it needs to be small in dimensions, battery operated and preferably to have wireless capabilities for mobile use. The fact that the nature of usage is either attached to or implanted in the human's body, requires the device to have very low power consumption in order to be efficient [7].

Very low power consumption is the primary criteria in biomedical devices and is the driving motivation for this research. This research involves the design of circuits that enable dynamic power management and dynamic leakage current management or schemes, combined with low power logic design techniques at processor logic core level, for CMOS biomedical devices.

#### 1.3 Research Objectives and Aims

The objective of this research is to design and implement power management schemes that will minimise power usage for application in biomedical devices. The specific aims of this research are:

- To investigate CMOS transistor behaviour in the ultra low operating region for biomedical devices,

- To develop ultra low power logic techniques,

- To design and implement dynamic voltage supply  $(V_{dd})$  scaling to reduce dynamic power dissipation,

- To design and implement dynamic threshold voltage  $(V_t)$  scaling to reduce static power dissipation, and

- To analyse the performance of the combined power management schemes on a Fast Fourier Transform processor core.

### 1.4 Research Design Methodologies and Techniques

The proposed research methodology and techniques to accomplish the afore mentioned aims are as follow:

• Investigate transistor behavior in the low operating region (subthreshold).

Since minimisation of power is the primary aim of this research, the starting point for ultra low power design is to investigate transistor behaviour and characteristics in the low operating region (subthreshold). An extensive literature review regarding the source of power dissipation has been undertaken prior to proceeding with the design step. The CMOS transistor's power dissipation characteristics, behaviour analysis and performance limitations in subthreshold region were investigated by applying different biasing techniques. The design and implementation was performed using Electronic Design Automation (EDA) tool sets from the Cadence Corporation.

• Develop and investigate low power logic techniques

Ultra low power logic techniques were developed to reduce power dissipation as well leakage current. The analysis of biasing techniques in the subthreshold region was used to develop ultra low power logic schemes. The first step was to investigate and combine several structures, power reduction techniques and range of power reduction values achievable. The most suitable structure combinations were chosen, developed and analysed for their use in the core design of biomedical applications. This step was repeated to develop a small component library using a combination of material parameters together with a range of values in the CMOS fabrication process. The designs and their implementation were performed using Electronic Design Automation (EDA) tool sets from the Cadence Corporation.

• Design and implementation of dynamic supply voltage scaling

A dynamic supply voltage ( $V_{dd}$ ) scaling module makes use of a clock frequency signal from the processor block. The module scales the power supply up or down, based on the clock signal. In designing dynamic  $V_{dd}$  scaling, initially a virtual clock is given to the input and an observed stable analog voltage output must be maintained. Since the dynamic  $V_{dd}$  scaling circuit controls the power supply of the whole core circuitry, careful attention must be given to the current driving capability of the design. The dynamic  $V_{dd}$  scaling was designed to respond at different frequencies and the performance was analysed. The selected design was optimised for performance in terms of minimizing power consumption and reducing physical area of the circuit.

• Design and implementation of dynamic threshold voltage scaling.

Designing a dynamic threshold voltage  $(V_t)$  scaling block is critical, as the leakage current is the main factor in static power consumption. Firstly, an appropriate transistor technology model library must be used. Secondly, the  $V_t$  scaling itself acts as a leakage current monitor (LCM) block, so preferably the same transistor technology model as the core logic is needed. The selected design was optimised for performance in terms of minimizing power consumption and reducing physical area of the circuit.

• Performance analysis of the dynamic power management scheme.

The performance of the power management chip was analysed with the respective FFT core logic, and compared in terms of reliability, speed, and power dissipation reduction.

### 1.5 Originality of the Thesis

In this dissertation the design and implementation of a low cost, low power, power management schemes for biomedical devices has been addressed. This research therefore represents a contribution of knowledge to integrated circuit power management in following key areas:

**Power**: Power reduction in dynamic and static power domains is the main topic in this thesis. Improved power management reduces the power dissipated in the biomedical device.

**Performance**: Bigger computation tasks require the processor to work harder, whilst smaller tasks do not require the processor to work at the same performance levels. The

performance of any particular device can now be varied according to the computation tasks, thereby improving the efficiency.

**Weight**: Portability of biomedical devices is one of the issues being addressed in this thesis. Improvement in transistor technology used for the development of biomedical devices reduces the physical size and weight of the device.

**Functionality**: Power management schemes allow a reduction in the power and heat generated by the device. As a result more functionality can be added onto the chip which reduces the risk of overheating.

**Cost**: A biomedical device designed using CMOS technology has the potential advantage of lower production costs.

#### 1.6 Thesis Organisation

The Thesis is organised into 9 chapters. Chapter 2 introduces the literature review and the background of this research. Several approaches to low power design are reviewed. In Chapter 3, low-voltage CMOS implementations of the three basic switching regulator topologies - buck, boost, and buck-boost - are introduced. A mathematical model is developed to estimate the overall battery run-time enhancements that can be effected by DC-DC converters. The requirements imposed on these regulators by the portable environment are described. Design equations and closed-form expressions for losses are presented for both pulse-width and pulse-frequency modulation schemes. Alternative regulator topologies which may find use in ultra-low-power applications where voltage conversion or regulation is required are introduced. Chapter 4 and 5 discuss the design techniques of each module involved in DC-DC conversion technique and voltage scaling, respectively. Mathematical models and simulation results of the optimized modules are presented. Chapter 6 discusses the possibility of applying threshold scaling in conjunction with voltage supply scaling for better performance, while Chapter 7 discusses the implementation aspect of the designed threshold scaling scheme to reduce static power dissipation. Chapter 8 discusses the integration results and layout implementation of the schemes in a FFT system. Chapter 9 is a conclusion which include of discussion of possible further work.

### 1.7 Conclusion

This research dissertation is an exploration of transistor, circuit, architectural and system-level considerations of a power management chip for energy reduction. Many concepts described here are specifically targeted to Biomedical device applications or processor systems, where the key metric is energy-efficient computation and other traditional metrics such as clock frequency or performance, latency and device physical area may need to be traded in order to achieve energy efficiency.

# Chapter Two: Motivation and Defining Parameters

#### 2.1 Home Care System

#### 2.1.1 Introduction

The world's future demographic indicates two major phenomena, an aging population due to increased life expectancy, and Baby Boomers demographic peak. According to the U.S Bureau of Census statistic alone, life expectancy has significantly increased from 49 years in 1901 to 77.6 years in 2003, and the number of people aged 65 and older is expected to increase from 35 million to 70 million by 2025. This projects that the worldwide population of people aged 65 and over, will rise from 357 million in 1990 to nearly 761 million by 2025.

The demand for healthcare in Australia is escalating; patients and government continue to be frustrated by the long waiting lists due to lack of medical professionals or infrastructure [5, 11]. This is an ongoing problem despite significant injections of government funds into the health industry.

#### 2.1.2 Medical monitoring Systems

For a long time, humans have dreamed of monitoring body functions and performing surgical procedures with tiny electronic systems. Monitoring body functionality has become a vital tool for medical diagnosis. For example, the conventional process of repeated mandatory measurement of blood pressure at short intervals increases the stress level of patients and consequently may falsify the results.

The key enabling factor in the monitoring system is the personal wearable health monitoring system. Wearable health monitoring systems integrated into tele-medical systems enable early detection of abnormal health conditions and the prevention of serious consequences [12-15]. Patients benefit from continuous real time monitoring as part of the diagnostic process, optimal monitoring those with chronic conditions or during their recovery from post acute surgical treatment.

#### 2.1.3 What is being Monitored?

In general, medical monitoring systems have been used for the following applications:

- Vital health signs monitoring is the main priority such as the patient's temperature, respiration, pulse, and blood pressure.

- Falling/Accident monitoring is another important detection for the elderly. This type of monitoring is essential as many elderly patients may suffer tremendously from a fall, which is caused by increasing instability due to age or other health conditions.

- Patients located at home, or at health care facility, need to be monitored for emergency events.

- Monitoring patients with cardiac disease, hypertension, diabetes, asthma, post stroke pain management, obesity, post surgical care and surveillance.

Traditionally, personal wearable medical monitoring systems have been implemented to collect data for offline processing. These systems incorporate multiple wired electrodes attached on a patient's body being connected to the monitoring system, which limit the patient's activity, mobility and level of comfort, thereby negatively influencing the measured results [16]. The development of the Personal Area Network (PAN) or Body Area Network (BAN) enables the possibility of integrating wearable health-monitoring devices into a patient's clothing [17]. However, the system is not robust enough for lengthy, continuous monitoring during normal physical activity [18], intensive training or computer-assisted rehabilitation [19].

Recent technological breakthroughs in microelectronic fabrication [20], wireless networking [21] together with integration of physical sensors, processors and radio interfaces/protocol on a single chip, promise a new generation of wearable wireless sensors suitable for many applications [22]. New generation wearable wireless systems are the primary area of application in this research, where many optimisation techniques and issues need to be addressed.

#### 2.1.4 Home Tele-care System

The evolvement of healthcare industry is triggered by advances in pervasive computing and Information and Communication Technologies (ICT), supported by technology advancement and miniaturisation of health care devices. The combination of these fields establishes potential for the development of a product which allows patients to have greater control of their personal health via delivery of health care at home (tele-care). This increasingly popular system architecture is applied for tele-care delivery by using pervasive computing at home. The key components in the architecture are: an intelligent health sensor, home healthcare servers, health care service providers (healthcare centres), telecommunication technology and devices, as depicted in Figure 2.1.

The figure shows the relationship between different technologies which not only need to be integrated together under strict health regulations and specifications, but also to maintain high quality delivery of service to patients.

Figure 2.1: Home healthcare system showing a personal network attached to a patient body, together with its supporting system and connection to a health service provider.

### 2.1.5 Essential Home Health Care System Building Blocks

#### 2.1.5.1 Health Sensory and Personal Server

A Wireless Body Area Network (WBAN) consists of a number of health sensors, which are combined to obtain the required patient information. Examples of such health sensors may include the following:

- Sensors for electrocardiogram, monitoring heart activity

- Sensors for electromyography, monitoring muscle activity

- Sensors for electroencephalography, monitoring brain electrical activity

- Blood pressure sensor

- Tilt sensor, monitoring trunk position

- Breathing sensor

- Movement sensors for analysing patient's activity

These sensors generate analog signals, which are continuously sampled, processed and delivered via a wireless network for further computation or storage. Furthermore, the health sensors are interfaced to a pre-processing/sampling module, whose task is to provide on-sensor processing capability and wireless communication protocols, so a single wireless network can be shared by multiple health sensor nodes. These wireless sensor nodes can be implemented as tiny external patches or embedded into the patient's attire. Therefore, these wireless sensor nodes should have minimal weight, size and power dissipation to prolong the continuous monitoring operation of the system. The current wireless sensor node continuously collects and processes a patient's body information, store them locally, and send them to the personal server. However, the sensor node should be able to vary the sampling, processing, transmitting capability according to the nature of the healthcare application in order to significantly reduce power consumption, thus extending battery life.

The information collected by the sensor node is further processed by the personal server. The personal server's other tasks are to synchronise and configure the WBAN nodes, monitor functionality of the nodes, and to act as the communication gateway to a remote healthcare provider.

#### 2.1.5.2 Telecommunications

There are two types of telecommunication networks required in a wireless homecare system, an external and an internal network. The external network is responsible for transmitting the processed health information of the patient from home to the health care provider. In general, the current telecommunication technology available for home tele-care systems include, public switched telephone networks, Integrated Services Digital Network (ISDN), satellite, wireless networks, leased line, cable and Asymmetric Digital Subscriber Line (ADSL). Currently in Australia, ADSL and cable, which are marketed as broadband connection, are the most viable options for a home

tele-care system. In remote areas where broadband connection is not available, satellite connection can be used.

The internal network enables intercommunication between the connected wireless nodes and the personal server. The existing telemetric devices use wireless communication channels exclusively to transfer data from the sensors to the monitoring station (personal server). They either transmit raw data or use more advanced protocols such as Bluetooth® that are too complex, power demanding and prone to interference by other devices operating in the same frequency range. These characteristics limit the prolonged use of the wireless wearable health device in terms of battery life [23, 24].

#### 2.1.5.3 Medical Service Providers

The healthcare provider collects data from individual patients, integrates the data into patient's medical record, processes them, and if necessary gives advice to the patients. If the received patient's health information indicates an imminent medical situation an emergency service can be notified. Storing patient's medical history in electronic medical form for future analysis must also be made available by the healthcare providers. Security and privacy of data is a significant issue in this area.

#### 2.1.5.4 System Design Issues

A home tele-care system integrates various aspects of technology with physical behavioural patterns which creates an inherently complex system. As WBAN and sensor nodes are the heart of the system, it is very important to analyse the technical aspects required and issues that might arise in the system design.

The main system design issues to enable the collection and delivery of patient's data in the system are:

• Advanced telecommunications, to ensure rapid and secure transmission of medical information

- Very low power radio frequency (RF) schemes

- Very low power data acquisition or personal health monitoring sensor network.

- Advanced or alternative power supply/source for the system

- Miniaturisation

Currently technology advances in Integrated Circuits (IC) allow designers to develop systems with low power and small system size, which fit well with the demands of wireless sensor networks. Recent developments in low power sensor communication networks, such as Zigbee®, have improved the bandwidth and data rate performance for sensor node networks.